FPGA, ASIC, SoC开发

自动化您的工作流程—从算法开发到硬件设计和验证

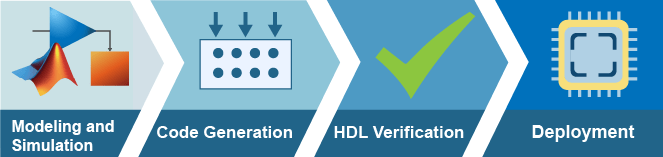

使用MATLAB®和仿真软件®开发在FPGA、ASIC和SoC设备上部署的原型和生产应用程序。使用MATLAB和Simulink,您可以:

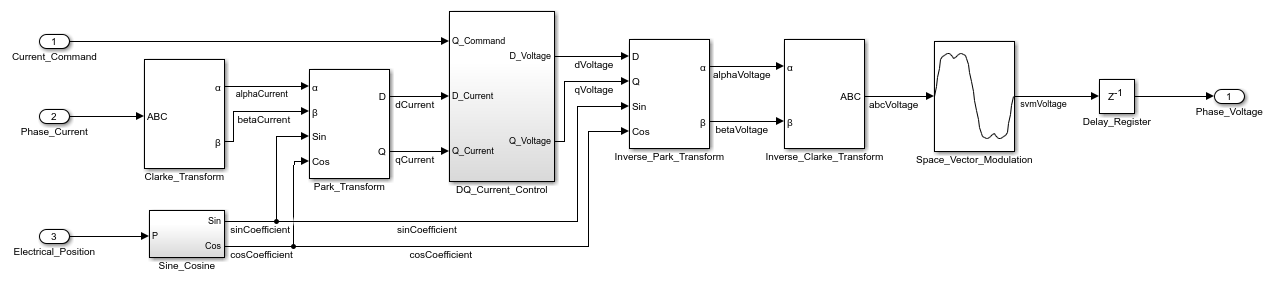

在抽象的高水平上对数字、模拟和软件进行建模和模拟。

使用自动引导转换为定点,或为任何目标设备生成本机浮点操作。

通过建模内存、总线和I/ o分析硬件和软件架构。

生成优化的,可读的,可跟踪的VHDL®或Verilog®用于数字逻辑的实现。

生成针对嵌入式处理器的处理器优化的C/ c++代码。

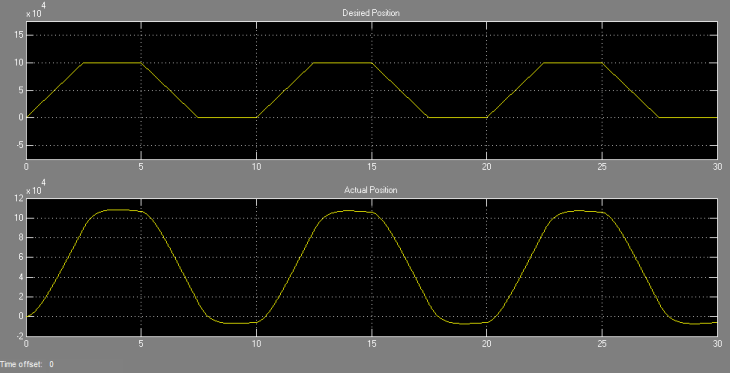

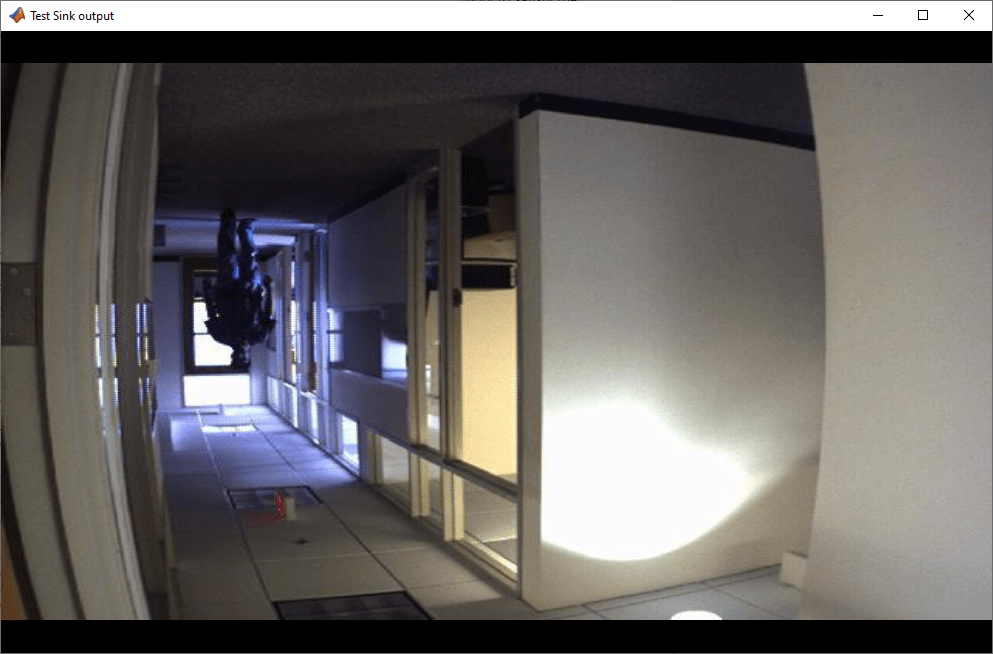

验证您的算法运行在HDL模拟器或FPGA或SoC设备上,该设备连接到您的MATLAB或Simulink测试台架。

2022世界杯八强谁会赢?用于FPGA、ASIC和SoC开发的产品

主题

建模与仿真

- 使用Simulink模板生成HDL代码(高密度脂蛋白编码器)

使用Simulink模型模板为HDL代码生成创建高效的硬件设计。 - 使用模板创建SoC模型(SoC Blockset)

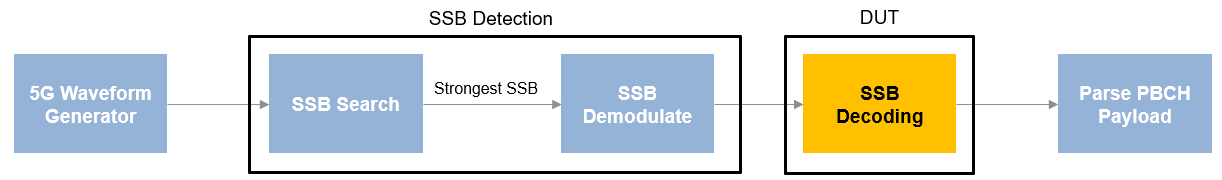

使用Simulink Project模板创建SoC模型。 - asic, fpga和soc的无线通信设计(高密度脂蛋白编码器)

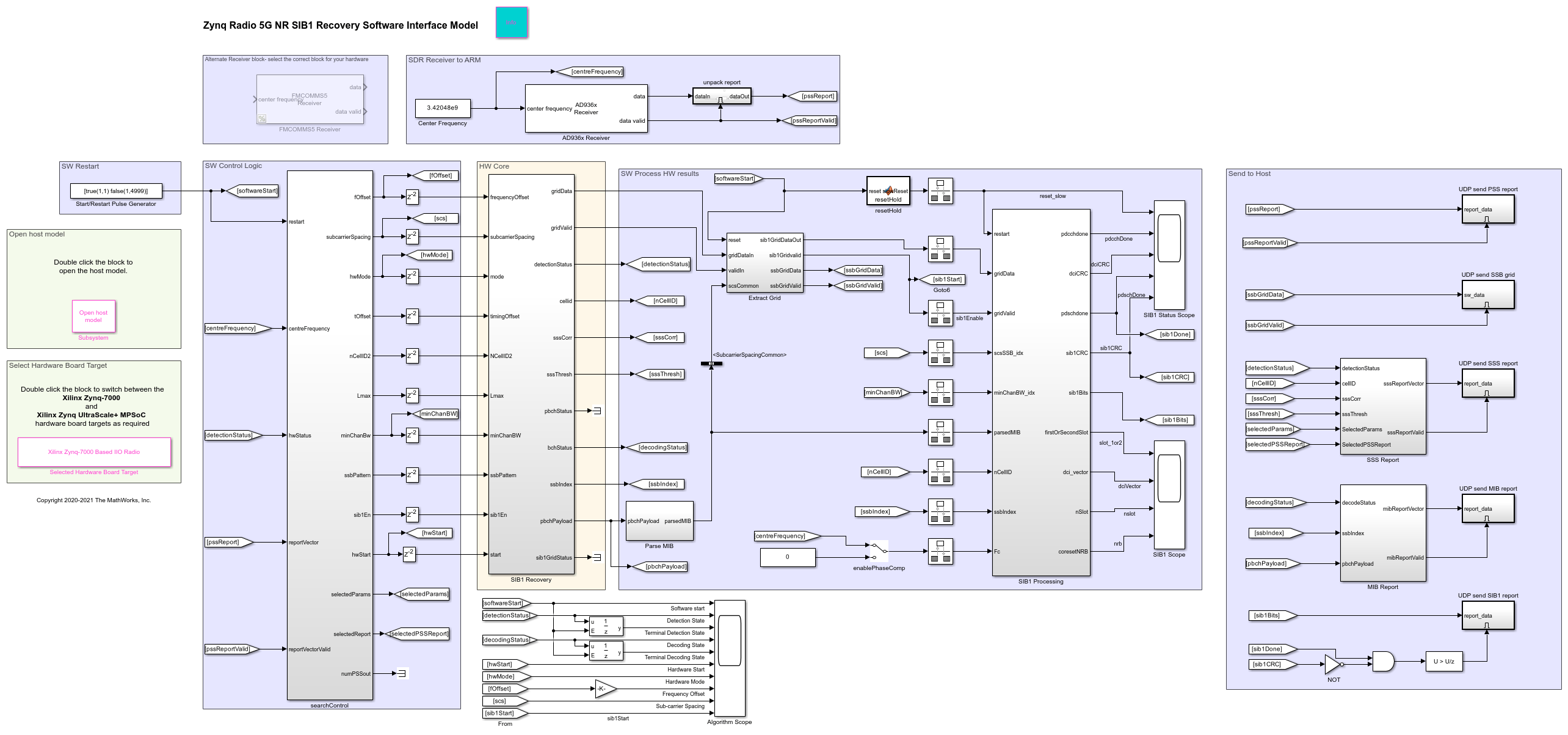

通过使用无线HDL工具箱™块设计硬件的无线通信算法。 - 实现FPGA的数字下变频(DSP HDL工具箱)

为fpga上的LTE设计一个数字下变频(DDC)。 - 高密度脂蛋白OFDM接收机(无线HDL工具箱)

实现基于ofdm的无线接收机硬件优化。 - 将MATLAB视觉算法转换为面向硬件的Simulink模型(视觉HDL工具箱)

在Simulink中创建一个硬件目标设计,实现与MATLAB参考设计相同的行为。

验证

- 开始使用Simulink HDL Cosimulation(高密度脂蛋白校验)

在Simulink®环境中使用Cosimulation Wizard建立一个HDL Verifier™应用程序。 - FPGA-in-the-Loop模拟(高密度脂蛋白校验)

fpga -in- loop (FIL)仿真提供了使用Simulink或MATLAB软件对任何现有HDL代码在真实硬件中测试设计的能力。 - 数据采集流程(高密度脂蛋白校验)

从FPGA上运行的设计中捕获信号数据。 - 使用基于jtag的AXI Manager访问FPGA内存(Xilinx FPGA板HDL验证器支持包)

使用基于jtag的AXI管理器访问连接到FPGA的内存。 - UVM组件生成概述(高密度脂蛋白校验)

从Simulink模型生成一个通用验证方法(UVM)环境。 - 生成SystemVerilog DPI组件(高密度脂蛋白校验)

从Simulink中生成DPI组件,并探索各种配置参数。

代码生成和部署

- 基本HDL代码生成工作流(高密度脂蛋白编码器)

遵循来自MATLAB和Simulink算法的HDL代码生成和FPGA合成的工作流程。 - 在Zynq工作流中使用axis - stream接口部署模型(高密度脂蛋白编码器)

使用AXI4-Stream接口在Zynq上的处理器和FPGA之间实现高速数据传输®硬件。 - 自定义IP核生成(高密度脂蛋白编码器)

使用HDL Workflow Advisor从模型或算法生成一个自定义IP核。 - 开始使用HDL工作流命令行界面(高密度脂蛋白编码器)

使用HDL工作流顾问从命令行和出口到脚本选择。 - 使用SoC Builder生成设计(用于Xilinx设备的SoC块集支持包)

生成SoC设计并在目标硬件板上运行SoC建设者工具。 - FPGA和SoC设备上的原型深度学习网络(深度学习HDL工具箱)

加速运行在固定比特流上的自定义深度学习网络的原型、部署、设计验证和迭代dlhdl。工作流对象。