FPGA和SoC硬件概述

通过遵循专门在硬件上设计和部署算法的步骤,以FPGA或SoC设备为目标。你从Simulink开始®模型或MATLAB®功能,选择一个硬件平台的目标,并遵循硬件-软件协同设计工作流程。通过重复执行这些步骤,探索划分和部署设计的最佳方法。

选择你的目标平台。在Simulink或MATLAB函数中对设计建模后,确定要将设计部署到哪个目标平台。考虑:

您希望针对哪种类型的设备:独立FPGA、SoC设备,还是具有独立FPGA和处理器的平台?

设备类型 推荐的工作流程 独立的FPGA 如果只部署到FPGA,请只使用硬件-软件协同设计工作流的第一部分:用于FPGA的原型和部署HDL算法。 SoC设备 要将模型部署到SoC设备,需要对设计进行分区,以包含用于FPGA的硬件部分和用于处理器的嵌入式软件部分,称为硬件-软件模型。FPGA需要一个比特流来改变它的物理连接(模型的硬件部分),而处理器需要一组以可执行文件形式出现的新指令(模型的软件部分)。 仿真软件实时™FPGA I/O模块 这种类型的平台指的是Speedgoat®目标机(作为处理器)和FPGA IO模块。您可以使用目标FPGA和SoC硬件步骤对FPGA和处理器进行编程。有关更多信息,请参见Speedgoat simulink -可编程I/O模块IP核生成工作流. 你处于开发的哪个阶段:快速原型还是生产?

为了快速创建原型,可以通过选择HDL Coder™支持的现有目标设备来节省开发时间。然后,您可以立即开始使用硬件-软件协同设计工作流。看到HDL编码器支持的硬件.

对于生产,或使用不受支持的设备进行快速原型设计,请首先创建自定义硬件平台,然后遵循硬件-软件协同设计工作流。看到创建自定义硬件平台.

硬件软件合作设计

硬件-软件协同设计工作流分为两个阶段:

FPGA的HDL算法原型和部署

为在目标硬件上部署模型做好准备。HDL Coder生成一个IP核和位流,其中包含从您的设计中生成的HDL代码,以部署到设备的FPGA。然后,您可以运行并验证IP核是否在目标硬件上工作。此阶段可用于针对独立FPGA设备、SoC设备或具有独立FPGA和处理器的平台。

为处理器部署C算法

通过配置FPGA和处理器之间的连接来配置硬件-软件接口,为处理器生成C代码。

将已划分为硬件和嵌入式软件组件的设计部署到包含FPGA和嵌入式处理器的平台上,例如SoC设备。该设计由DUT算法和软件组件组成,DUT算法为其生成一个IP核和一个包含HDL代码的比特流,软件组件为其生成在处理器上运行的嵌入式代码。您使用生成的软件接口模型和IP核(包括硬件接口组件,例如AXI接口)在硬件和软件组件之间进行接口。

FPGA的HDL算法原型和部署

为部署准备模型

对于可部署到目标设备上的算法模型和设计,以下是高级任务:

如果您使用的平台包含处理器和FPGA(如SoC设备),则为目标硬件的硬件和软件组件划分设计。您可以对设计进行分区,以生成针对FPGA的硬件和在嵌入式处理器上运行的软件。

将模型的输入和输出映射到硬件接口,例如AXI4接口、按钮和led。生成的设计在部署时可以与硬件系统的其余部分通信。有关更多信息,请参见目标平台接口.

有关为部署准备模型的示例,请参见着眼于Xilinx Zynq平台.

生成IP核和比特流

一旦你的设计准备好部署,你可以使用HDL工作流顾问:

生成一个通用的独立于董事会的Xilinx®或英特尔®HDL IP核。IP核是一个可共享和可重用的HDL组件,它实现了特定的功能,通常是一种算法。IP核由IP核定义文件、为算法生成的HDL代码、包含寄存器地址映射的C头文件和IP核报告组成。有关示例,请参见利用Simulink模型生成与板无关的HDL IP核.

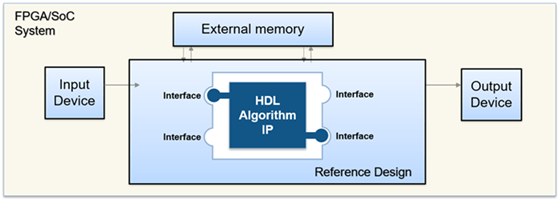

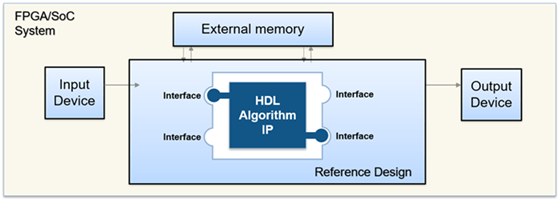

通过使用Xilinx Vivado将IP核集成到参考设计中,以针对独立FPGA板或SoC平台®IP积分器或英特尔Qsys。参考设计包含英特尔或Xilinx软件将设计部署到SoC平台所需的元素,但从硬件-软件模型生成的自定义IP核和嵌入式软件除外。参考设计充当了一个在硬件平台之上构建算法的平台,并抽象了硬件平台,以便您可以专注于算法开发。一旦您完成了算法开发,HDL Coder使您能够将算法打包为IP核,并使其适合参考设计。

生成一个包含IP核的位流,用于在目标FPGA上部署。

有关生成IP核和比特流的示例,请参见用MATLAB生成FPGA板上LED闪烁的IP核.

在目标硬件上运行并验证IP核

在目标硬件上运行并验证从IP核设计生成的比特流:

通过将目标硬件连接到主机来准备目标硬件。如果您正在使用包含FPGA和处理器的平台,例如SoC设备,请下载用于处理器的Linux映像。有关更多信息,请参见引导SD卡设置(Xilinx Zynq平台HDL编码器支持包)Xilinx Zynq公司®平台或引导SD卡设置(用于Intel SoC设备的HDL编码器支持包)用于英特尔SoC设备。

建立从主机到目标硬件的JTAG或以太网连接。

为目标设备编程。

通过使用以下原型方法之一在目标硬件上对设计进行原型化、调试和验证:

FPGA的I / O。您可以使用HDL Workflow Advisor生成的主机接口模型或主机接口脚本在运行MATLAB和Simulink的主机PC与部署在FPGA上的生成的IP核之间进行通信。

AXI经理

FPGA数据采集

FPGA-in-the-Loop (FIL)

软件接口模型生成,参见配置FPGA软件接口.

有关示例,请参见基于MATLAB命令的实时数据硬件FPGA原型设计.

为处理器部署C算法

配置FPGA软件接口

为了实现一个完整的硬件-软件系统,HDL Workflow Advisor从原始的Simulink模型生成一个软件接口模型。该软件接口模型可用于部署到目标平台的板载处理器。此模型包含为SoC设备或目标平台上的处理器正确配置的设备驱动程序。如果您的目标是SoC设备,则此模型是硬件-软件设计所需的第二种模型。第一个模型是原始模型,使用针对板载FPGA的HDL算法。该软件接口模型以处理器为目标,并在部署到处理器的软件和部署到FPGA的生成IP核之间进行通信。

有关更多信息,请参见生成软件接口模型来探测和快速原型HDL IP核.

硬件软件部署

生成C代码(需要嵌入式编码器®),并使用外部模式或处理器在环(PIL)模式在目标硬件上部署和运行硬件-软件模型。SoC设备的可部署设计包括:

从您的原始模型生成的位流,包含您的HDL IP核。

一个软件接口模型,包含配置的设备驱动程序,允许处理器和FPGA之间的通信,以及用于嵌入式处理器的C代码生成。

将您的完整分区设计部署到生成的处理器C代码(来自软件接口模型)和用于板载FPGA的位流(来自包含IP核的原始模型),使您能够在SoC或芯片上运行算法实时仿真软件具有FPGA I/O板的目标机器。

有关示例,请参见使用HDL编码器和嵌入式编码器调试Zynq设计.

创建自定义硬件平台

如果您的硬件还没有可用的平台,您可以定义一个自定义硬件平台,以便与硬件-软件协同设计工作流一起使用。自定义硬件平台为定义硬件系统和部署设计提供了灵活性。例如,当部署到生产硬件时,您可以定义一个自定义平台。创建硬件平台包括创建一个新的板定义来描述您的硬件,并为您的板创建一个或多个新的参考设计。您还可以为现有的电路板创建新的参考设计。

参考设计提供了算法IP核和硬件板之间的抽象级别,使设计要部署到硬件上的算法更容易、更高效。参考设计充当算法和硬件平台之间的层,您可以使用该层来利用硬件中的资源,而不必在设计中对这些特定的硬件资源建模。您可以专注于算法设计,而无需实现硬件的底层细节。您还可以将算法重新定位到不同的硬件。例如,当您从用于原型设计的评估板过渡到生产硬件时,您可以重新确定算法设计的目标。

有关更多信息,请参见电路板和参考设计注册系统.