SoC应用的系统工程方法

这个例子展示了如何使用系统工程方法在片上系统(SoC)平台上设计一个样本信号检测器应用程序。本例中的工作流将应用程序功能映射到所选硬件架构上。

信号检测器应用程序连续地处理信号数据,并将信号分为高频或低频。信号在高频和低频之间的变化不能超过1毫秒。信号以10mhz的频率采样。

功能体系结构

定义应用程序的功能体系结构。在这个阶段,还不知道应用程序组件的实现。您可以使用System Composer™软件来获取功能体系结构。

该模型表示功能体系结构及其主要软件组件及其连接。

systemcomposer.openModel (“soc_signaldetector_func”);

应用程序的功能架构由以下顶级组件组成:

产生信号

预处理信号

信号的分类

激活发光二极管

硬件体系结构

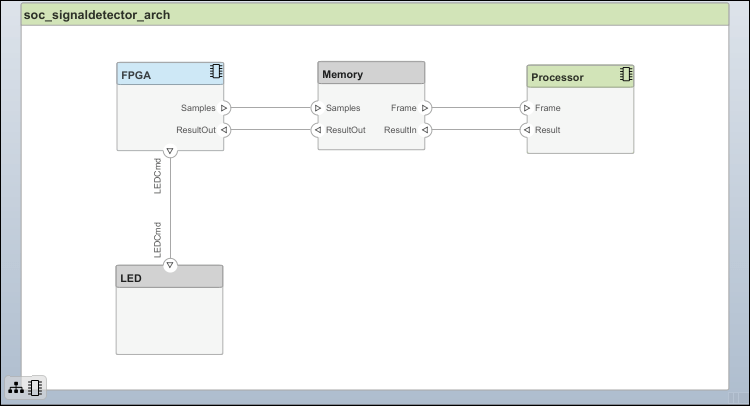

选择硬件架构。考虑到应用的复杂性,请选择SoC设备。所选SoC器件具有硬件可编程逻辑(FPGA)核心和嵌入式处理器(ARM)核心。您可以使用System Composer软件来获取硬件体系结构的细节。

该模型表示硬件体系结构及其主要硬件组件及其连接。

systemcomposer.openModel (“soc_signaldetector_arch”);

行为建模

如果功能组件的实现可用,则可以将它们作为行为添加到功能体系结构中。在System Composer中,对于每个功能组件,您可以将实现行为链接为Simulink®模型。要查看组件实现,双击功能体系结构模型中的每个组件。

在您定义了每个组件的行为之后,您可以模拟整个应用程序的行为并验证其功能正确性。选择运行在功能架构模型中。然后,对信号分类结果进行分析仿真数据检查.若要更改信号类型,请选择产生信号组件,然后选择手动开关块。确认源信号分类正确。

功能和硬件元素的分配

在细化功能和硬件体系结构之后,为不同的硬件元素分配不同的功能组件,以满足所需的系统性能基准。在这种情况下,一些功能组件在硬件架构中的实现位置受到限制。您必须实现产生信号而且激活发光二极管由于输入输出(I/O)连接,所选硬件架构中的FPGA核心上的组件。相对而言,您可以实现预处理信号而且信号的分类FPGA或处理器核心上的组件。

器件约束生成信号FPGA预处理信号-分类信号-激活led FPGA

此示例展示了如何使用三种可能的场景将应用程序功能体系结构分配到硬件体系结构。

FPGA负责预处理和分类。

FPGA处理预处理,处理器处理分类。

处理器处理预处理和分类。

System Composer将这些场景捕获为场景1,场景2,场景3使用配置编辑器(系统作曲家).

allocSet = systemcomposer.allocation.load (“soc_signaldetector_allocation”);systemcomposer.allocation.editor

选择分配场景需要找到最佳地满足应用程序需求的实现。通常你可以通过静态分析找到这个实现,而不需要详细的模拟。在本例中,使用静态分析来分析在处理器和FPGA上实现不同功能组件的计算成本。

实施成本

组件的实现成本取决于所需的计算操作。要确定实现成本,请考虑以下典型方法。

组件实现不可用:从可用的参考实现获取计算成本。

实现和硬件都是可用的:测量或分析候选硬件上的实现成本。

实现是可用的,但硬件是不可用的:通过使用SoC Blockset™算法分析器功能估计实现成本

socAlgorithmAnalyzerReport.

的socModelAnalyzer函数估计Simulink模型中的操作数量,并生成算法分析器报告。要获取模型执行的操作数量,然后分析处理器上的实现成本,请使用动态分析函数选项。要获得算法所需的运算符数量,然后在FPGA上分析实现成本,请使用静态分析功能选项。举例说明如何使用socModelAnalyzer,参见这个示例函数。

soc_signaldetector_costanalysis

***组件:'预处理信号' ADD(+) MUL(*) ______ ______ FPGA实现15 16处理器实现15300 16320 ***组件:'分类信号' ADD(+) MUL(*) ______ ______ FPGA实现32 18处理器实现32640 18360

在此代码中获得的每个功能组件的实现成本被输入到功能体系结构中相应的原型中。要验证这些值,请在功能架构模型中选择每个组件并使用Property Inspector。

要了解更多关于socModelAnalyzer,请参阅使用socModelAnalyzer比较FIR过滤器实现的例子。这个例子展示了如何分析一个Simulink算法的不同实现的计算复杂度。

配置选择

您可以使用实现应用程序功能组件所需的操作符或操作的数量来决定如何将功能组件分配给硬件组件。通过将实现成本与FPGA和处理器的可用资源进行比较,分析候选分配。本例使用FPGA中的样例值和硬件架构模型中的处理器组件来获得可用的计算资源。通过使用属性检查器验证值。

通常,分析不直接使用运算符或操作的数量。相反,运算符或操作的数量乘以每个运算符或操作的成本。操作或操作的成本取决于硬件。确定此类成本超出了本示例的范围。

关于如何使用成本模型的示例,请使用此函数。注意,我们要求FPGA和处理器的容量大于估计的实现成本,并且处理器净空在60%到90%之间。

soc_signaldetector_partitionanalysis

FPGA需求方(900)使用FPGA附近地区使用(218600)的处理器指令/ s(1000000000)的处理器净空(%)的可行性 ___________________________ _____________________________ ____________________________________________ ______________________ ________ 场景1 34 576 0 100 0场景2 16 192 326400000 100 0场景3 0 0 326400000 100 0

根据结果,方案2是可行的。

FPGA与处理器之间的数据路径设计

FPGA是逐样本处理数据,处理器是逐帧处理数据。由于处理器任务的持续时间可能不同,为了防止数据丢失,需要一个队列来保存FPGA和处理器之间的数据。在这种情况下,您必须设置这些与队列相关的参数:帧大小、帧缓冲区的数量和FIFO大小(即FIFO中的样本数量)。此外,在嵌入式应用程序中,任务持续时间可能在不同的任务实例之间有所不同(例如,由于不同的代码执行路径或由于操作系统切换时间的变化)。因此,数据可能被丢弃到内存通道中。的数据从硬件流到软件示例展示了选择前面提到的满足应用程序需求的参数的系统方法。