冷杉杀害多人者

有限脉冲响应(FIR)抽取滤波器

- 库:

DSP HDL工具箱/滤波

描述

的冷杉杀害多人者块实现了为HDL代码生成而优化的单速率多相FIR抽取滤波器。该模块提供了一个硬件友好的接口,具有输入和输出控制信号。为了对生成的HDL代码提供周期精确的模拟,该块对体系结构延迟进行了建模,包括管道寄存器和资源共享。

该块接受标量或向量输入。当使用向量输入且向量大小小于抽取因子时,抽取因子必须是向量大小的整数倍。在这种情况下,输出是标量的,输出有效信号表示抽取后哪些样本是有效的。输出的数据每天都有效DecimationFactor/VectorSize样本。该波形显示了四个样本的输入矢量和八个抽取因子。输出数据是一个每秒钟循环有效的标量。

当使用向量输入且向量大小大于抽取因子时,向量大小必须是抽取因子的整数倍。在本例中,输出是向量VectorSize/DecimationFactor样本。该波形显示了8个样本的输入矢量和4个抽取因子。输出数据是每个循环中两个样本的向量。

该块提供两个过滤器结构。直接形式收缩架构提供了一种高效利用Intel的实现®和Xilinx®DSP块。这种体系结构可以是完全并行的,也可以是串行的。要使用串行体系结构,输入样本必须在有效样本之间用规则数量的无效循环隔开。直接形式转置架构是一种完全并行的实现,适用于FPGA和ASIC应用。对于将乘数器、管道寄存器和预加器匹配到FPGA供应商的DSP配置的过滤器实现,在生成HDL代码时指定目标设备。

所有的滤波器结构都通过共享对称或反对称滤波器的乘法器,以及删除零值系数的乘法器(如半带滤波器和希尔伯特变换)来优化硬件资源。

该块为输入向量中的每个样本实现一个过滤器。然后,通过及时交错子滤波器系数,该块在多相子滤波器之间共享该滤波器。

港口

输入

数据——输入数据

标量|向量

输入数据必须是实值或复值标量或向量。当使用向量输入且向量大小小于抽取因子时,抽取因子必须是向量大小的整数倍。当使用向量输入且向量大小大于抽取因子时,向量大小必须是抽取因子的整数倍。向量的大小必须小于等于64。

当输入数据类型是整数类型或定点类型时,块使用定点算法进行内部计算。

双而且单数据类型支持模拟,但不支持HDL代码生成。

数据类型:不动点|单|双|int8|int16|int32|uint8|uint16|uint32

复数的支持:是的

有效的—表示有效的输入数据

标量

指示输入数据是否有效的控制信号。当有效的是1(真正的),该块从输入中获取值数据端口。当有效的是0(假),块忽略来自输入的值数据端口。

数据类型:布尔

输出

数据-过滤输出数据

标量

过滤的输出数据,作为实值或复值标量返回。当输入数据类型为浮点类型时,输出数据继承输入数据的数据类型。当输入数据类型是整数类型或定点类型时,则输出的参数数据类型TAB指定输出数据类型。

输出有效的信号表示抽取后哪些样本是有效的。当输入向量大小大于抽取因子时,输出向量为VectorSize/DecimationFactor样本。

数据类型:不动点|单|双

复数的支持:是的

有效的—表示有效的输出数据

标量

控制信号,指示数据是否从输出数据港口是有效的。当有效的是1(真正的),块从输出返回有效的数据数据端口。当有效的是0(假),从输出的值数据端口无效。

数据类型:布尔

参数

主要

系数- FIR滤波器系数

fir1(35岁,0.4)(默认)|实值或复值向量

FIR滤波器系数,指定为实值或复值向量。可以将vector指定为工作空间变量或对筛选器设计函数的调用。当输入数据类型是浮点类型时,块将系数转换为与输入相同的数据类型。当输入数据类型是整数类型或定点类型时,可以为的系数设置数据类型数据类型选项卡。

例子:Firpm (30,[0 0.1 0.2 0.5]*2,[1 1 0 0])使用线性相位滤波器设计函数定义系数。

数据类型:单|双|int8|int16|int32|uint8|uint16|uint32

复数的支持:是的

滤波器结构- HDL过滤器架构

直接形成收缩(默认)|直接形式转置

该块实现了多相分解滤波器离散冷杉滤波器块。这两种结构通过在输入向量中的每个样本的一个滤波器实现上交错子滤波器系数来共享资源。指定HDL过滤器体系结构为以下结构之一:

直接形成收缩-该体系结构提供了一个并行或部分串行的滤波器实现,可以有效地利用Intel和Xilinx DSP块。对于部分串行实现,请为有效输入样本之间的最小循环数参数。不能在部分串行的体系结构中使用基于框架的输入。当有效输入样本之间的最小循环数大于1,则块选择产生最少乘数的过滤器体系结构。如果N允许在每个子过滤器中使用单个倍增器,然后块实现单个串行过滤器并抽取输出样本。

直接形式转置-该架构是一个完全并行的实现,适用于FPGA和ASIC应用。

所有实现通过在输入向量中的每个样本的一个过滤器实现上交错子过滤器系数来共享资源。

该块实现了多相分解滤波器使用离散冷杉滤波器块。有关体系结构的详细信息,请参见fpga和asic的FIR滤波器架构.

大量毁灭的因素——大量毁灭因素

2(默认)|大于2的整数

指定大于2的整数抽取因子。当使用向量输入且向量大小小于抽取因子时,抽取因子必须是向量大小的整数倍。当使用向量输入且向量大小大于抽取因子时,向量大小必须是抽取因子的整数倍。

有效输入样本之间的最小循环数-输入时序的串行化要求

1(默认)|正整数

输入计时的序列化要求,指定为正整数。这个参数代表N,有效输入样本之间的最小循环次数。要实现完全串行的体系结构,请设置有效输入样本之间的最小循环数大于过滤器长度,l,或者正.

该块在序列化之前应用系数优化,因此最终过滤器的共享因子可以低于您指定的循环数。

依赖关系

若要启用此参数,请设置滤波器结构来直接形成收缩.

不能使用基于框架的输入有效输入样本之间的最小循环数大于1。

数据类型

舍入模式-输出类型铸造的舍入模式

地板上(默认)|天花板|收敛|最近的|轮|零

类型指定的数据类型的舍入模式输出参数。当输入数据类型为浮点型时,块忽略此参数。有关更多细节,请参见舍入模式.

整数溢出时饱和-输出类型铸造溢出处理

从(默认)|在

类指定的数据类型对输出进行类型转换的溢出处理输出参数。当输入数据类型为浮点型时,块忽略此参数。有关更多细节,请参见溢出处理.

系数-过滤系数的数据类型

继承:与输入相同的字长(默认)|<数据类型>表达

该块将筛选器系数转换为此数据类型。量化舍入到最接近的可表示值并在溢出时饱和。当输入数据类型为浮点型时,块忽略此参数。

建议该参数的数据类型为继承:与输入相同的字长.

如果发生上述任何一种情况,该块将返回警告或错误。

系数数据类型没有足够的分数长度来准确地表示系数。

系数数据类型为无符号,且系数包含负值。

输出—过滤器输出的数据类型

继承:通过内部规则继承(默认)|继承:与输入相同的字长|<数据类型>表达

该块将筛选器的输出转换为此数据类型。的设置舍入模式而且溢出模式参数。当输入数据类型为浮点型时,块忽略此参数。

该块增加每个过滤器抽头内的全精度字长度,并将最终输出转换为指定的类型。最大最终内部数据类型(WF)取决于输入数据类型(WI),系数数据类型(WC),系数数(l),由

WF=WI+WC+装天花板(log2 (l)).

由于系数值限制了潜在的增长,通常实际的全精度内字长度小于WF.

控制端口

算法

该块实现了一个多相滤波器组,其中滤波器系数被分解为DecimationFactorsubfilters。如果过滤器长度不能被大量毁灭的因素参数值,则块零垫系数。当输入之间有规律的间隔,有效样本之间有两个或两个以上的循环时,如有效输入样本之间的最小循环数参数时,过滤器可及时共享乘数资源。

此流程图显示了由参数设置产生的过滤器体系结构。它还显示了过滤器实现使用的乘数的数量。过滤器架构取决于输入帧的大小,V,抽取因子,R,有效输入样本之间的循环次数,N,和滤波系数的个数,l.架构的顺序是从左边最低的资源使用到右边最高的资源使用。更高的资源体系结构正在为更高的吞吐量权衡资源使用。流程图下面描述了每个体系结构。

流程图中所示的乘数是用于具有实数输入和实数系数的滤波器。对于复杂的输入,滤波器使用三倍的乘数。

结构1 -完全平行的一抽头交错多相滤波器组。

当DecimationFactor大于过滤器长度,对于任何值NumCycles,该滤波器成为一个单点滤波器与交错系数,并使用单一乘法器。

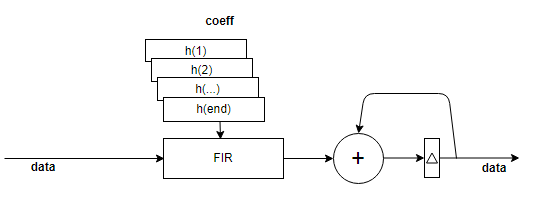

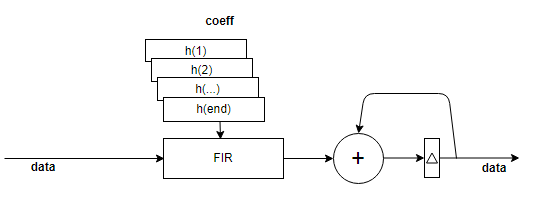

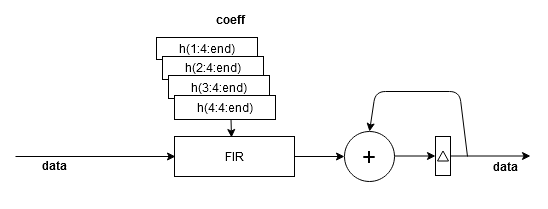

架构2 -单个全串行滤波器。

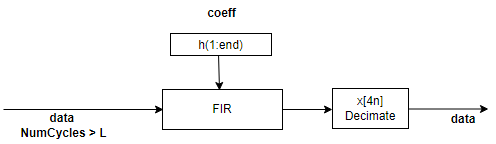

当过滤器有NumCycles大于过滤器系数的数量,块实现了一个单一的全串行过滤器,并通过抽取因子抽取输出样本。这个串行滤波器使用一个倍增器。

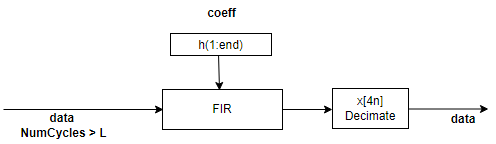

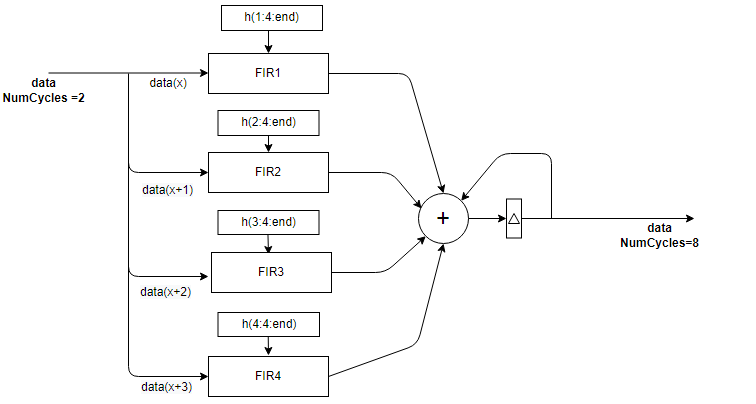

结构3 -部分串联多相滤波器组。

当过滤器有NumCycles大于1且小于滤波器系数数的块实现多相滤波器DecimationFactorsubfilters。此图显示了输入数据,每一秒循环一个有效样本和一个DecimationFactor的

4.输出数据每8个周期有一个有效样本。此筛选器实现使用FilterLength/NumCycles乘数。

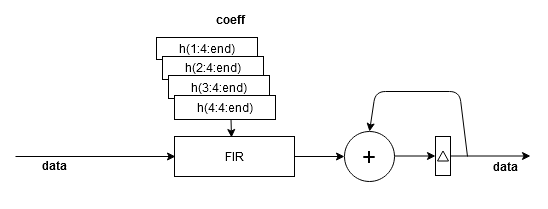

体系结构4 -完全并行多相交错滤波器组(标量)。

图中显示了带有标量输入的多相滤波器组,DecimationFactor设置为

4,NumCycles设置为1.四组分解系数在时间上交错在一个子滤波器上。输出数据样本每四个周期有效一次。过滤器使用FilterLength/DecimationFactor乘数。

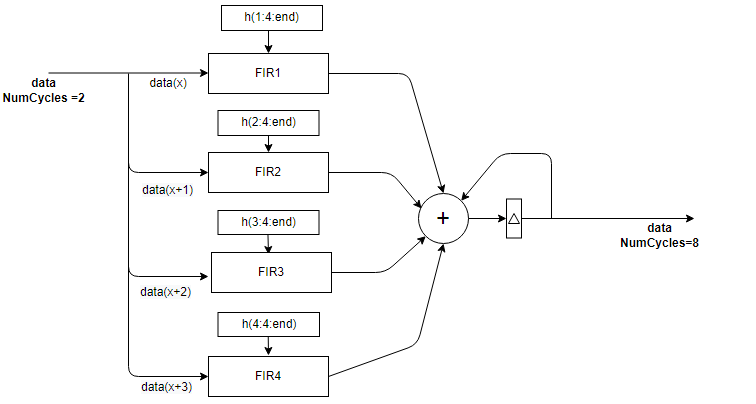

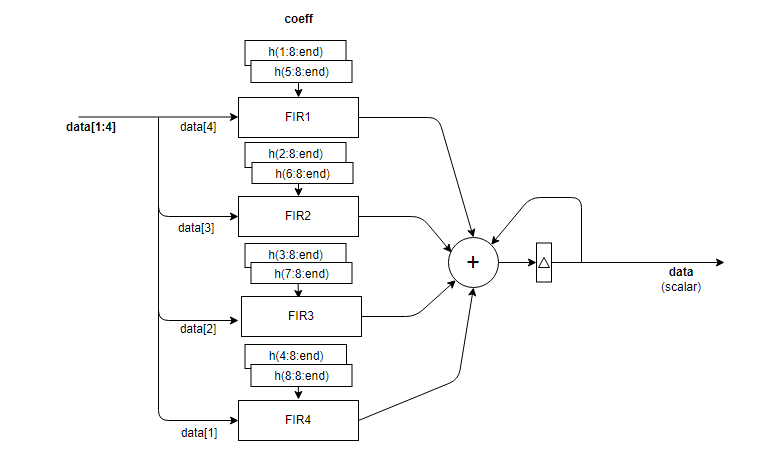

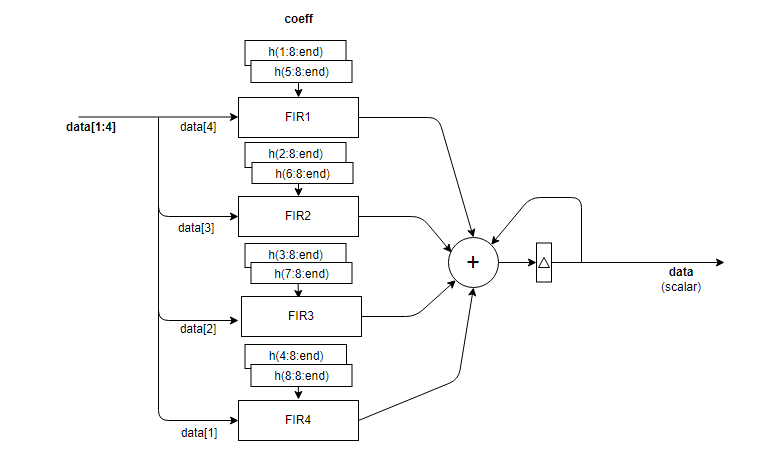

体系结构5 -完全并行多相交错滤波器组(矢量)

图中显示了输入矢量尺寸小于抽取因子的多相滤波器组。该过滤器的输入向量为四个值和DecimationFactor设置为8。四个子滤波器中的每一个都有两组时间交错的系数。过滤器使用InputSize*FilterLength/DecimationFactor乘数。

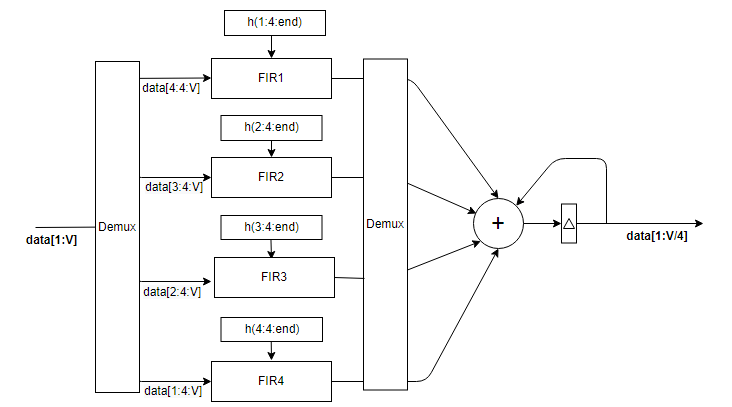

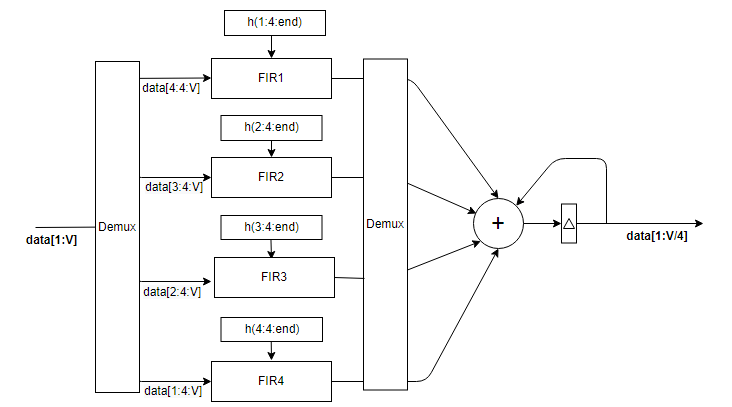

架构6 -完全并行框架的滤波器组

由于输入向量的大小大于抽取因子,该块实现抽取因子子过滤器,每个子过滤器具有基于帧的输入VectorSize/DecimationFactor样本。输出向量有VectorSize/DecimationFactor样本。过滤器使用InputSize*FilterLength/DecimationFactor乘数。

每个子过滤器都用离散冷杉滤波器块。输出端的加法器是流水线化的,以适应更高的合成频率。有关体系结构的详细信息,请参见fpga和asic的FIR滤波器架构.

请注意

的输出冷杉杀害多人者类的输出不匹配冷杉大量毁灭block from DSP System Toolbox™sample-for-sample。这种差异主要是由于在跨子滤波器应用样本时所处的阶段。匹配冷杉大量毁灭块,应用大量毁灭的因素- 1个0的冷杉杀害多人者在数据流开始时阻塞。

的冷杉大量毁灭Block还使用稍微不同的数据类型进行全精度计算。如果输出值超出内部数据类型,则不同的数据类型还可能导致输出值的差异。

性能

这个表显示了为默认的FIR抽取滤波器生成的HDL代码的综合后资源利用情况,使用标量输入、8的抽取因子、16位输入和16位系数。合成的目标是Xilinx ZC-706 (XC7Z045ffg900-2) FPGA。的全局HDL重置类型参数是同步,减少时钟使参数被选中。的重置端口是禁用的,因此只有控制路径寄存器连接到生成的全局HDL重置。

| 资源 | 使用 |

|---|---|

| 附近地区 | 676 |

| 片注册 | 878 |

| 片 | 257 |

| Xilinx LogiCORE DSP48 | 5 |

除去地点和路线,本设计的最大时钟频率为526mhz。

对于具有四元素输入向量的相同过滤器,该过滤器使用这些资源。

| 资源 | 使用 |

|---|---|

| 附近地区 | 322 |

| 片注册 | 2351 |

| 片 | 502 |

| Xilinx LogiCORE DSP48 | 20. |

除去地点和路线,本设计的最大时钟频率为518mhz。

对于相同的过滤器,标量输入和numCycles设置为4,过滤器将使用这些资源。

| 资源 | 使用 |

|---|---|

| 附近地区 | 835 |

| 片注册 | 1341 |

| Xilinx LogiCORE DSP48 | 8 |

除去地点和路线,设计的最大时钟频率为460 MHz。

扩展功能

C / c++代码生成

使用Simulink®Coder™生成C和c++代码。

该块支持用于Simulink加速器和快速加速器模式的C/ c++代码生成,以及用于DPI组件生成。

HDL代码生成

使用HDL Coder™为FPGA和ASIC设计生成Verilog和VHDL代码。

HDL Coder™提供了影响HDL实现和合成逻辑的额外配置选项。

| ConstrainedOutputPipeline | 通过在设计中移动现有的延迟来放置在输出上的寄存器数量。分布式管道不会重新分发这些寄存器。默认值是 |

| InputPipeline | 要在生成的代码中插入的输入管道阶段的数量。分布式流水和约束输出流水可以移动这些寄存器。默认值是 |

| OutputPipeline | 要在生成的代码中插入的输出管道阶段的数量。分布式流水和约束输出流水可以移动这些寄存器。默认值是 |

FIR Decimator块不支持通过HDL Coder设置进行资源共享优化。相反,设置滤波器结构参数部分连续收缩,并根据输入时间或资源使用情况配置序列化因子。

版本历史

介绍了R2020bR2022a:搬到DSP HDL工具箱从DSP系统工具箱

在R2022a之前,这个区块被命名FIR抽取HDL优化被包含在DSP系统工具箱中DSP系统工具箱HDL支持图书馆。

R2022a:串行收缩期架构

该块支持部分和完全串联的收缩结构。如果有效输入样例之间存在无效循环的常规模式,则此体系结构使您能够共享硬件资源。要使用串行收缩结构,设置滤波器结构来直接形成收缩而且有效输入样本之间的最小循环数到大于1的值。不能在串行体系结构中使用基于框架的输入。

R2022a:输入向量的大小可以大于抽取因子

在以前的版本中,块不支持大于抽取因子的输入向量大小。

MATLAB命令

你点击了一个对应于这个MATLAB命令的链接:

在MATLAB命令窗口中输入命令来运行该命令。Web浏览器不支持MATLAB命令。

您也可以从以下列表中选择网站:

如何获得最佳的网站性能

选择中国网站(中文或英文)以获得最佳的网站表现。其他MathWorks国家网站没有针对从您的位置访问进行优化。