## MathWorks Vision for Systematic Verification and Validation

Bill Aldrich

Senior Development Manager

Simulink Verification and Validation, Simulink Design Verifier

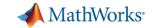

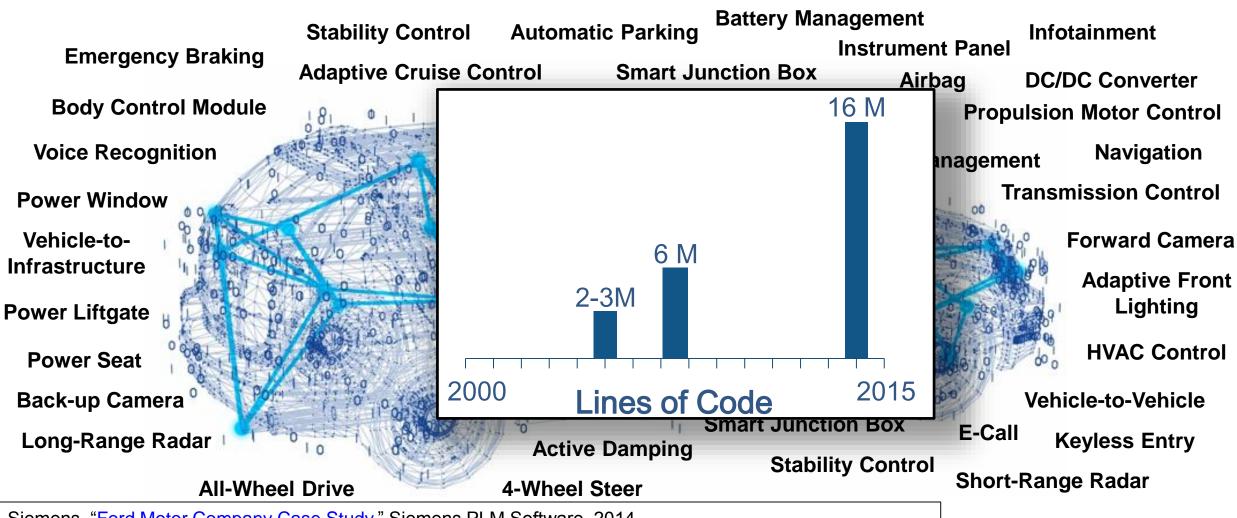

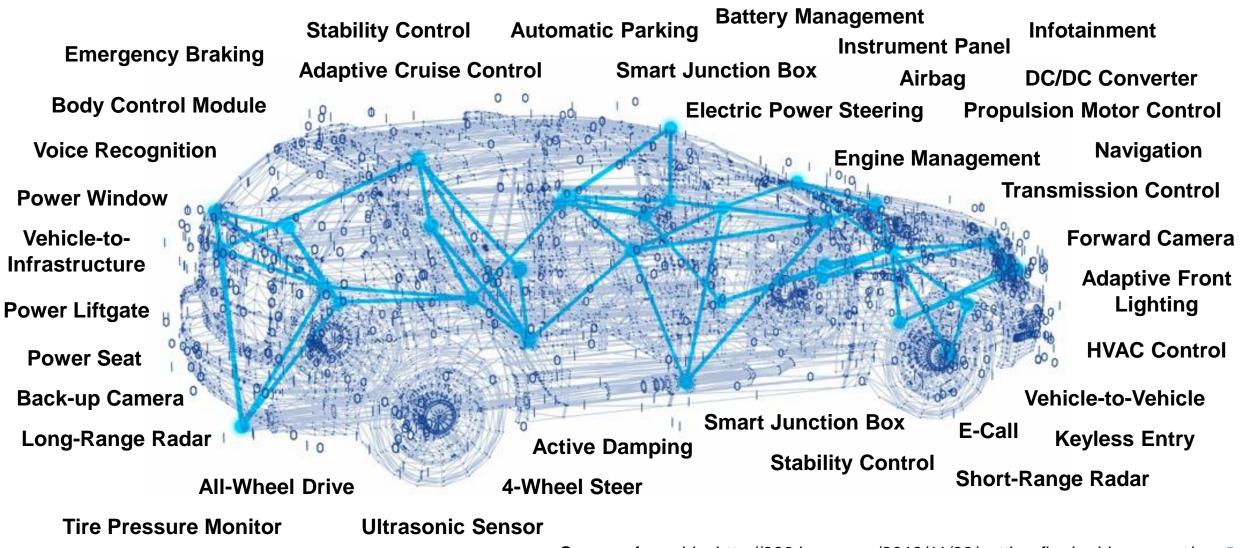

Siemens, "<u>Ford Motor Company Case Study</u>," Siemens PLM Software, 2014 McKendrick, J. <u>"Cars become 'datacenters on wheels', carmakers become software companies,"</u> ZDJNet, 2013

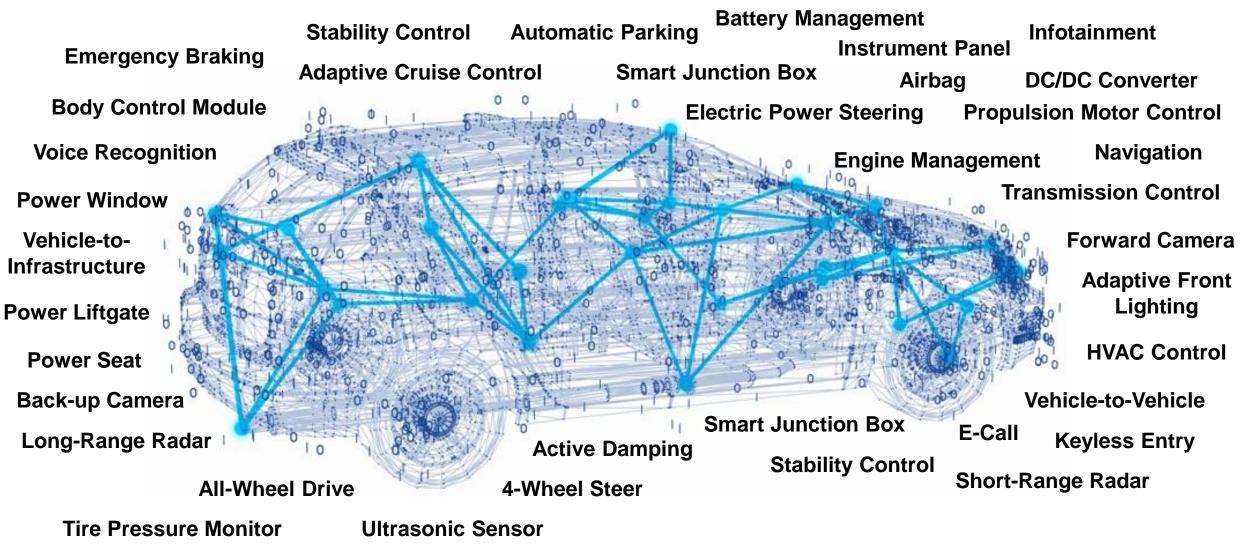

#### **Development Challenges**

- Representing complex systems

- Coordinating work across teams

- Working efficiently

- Ensuring quality

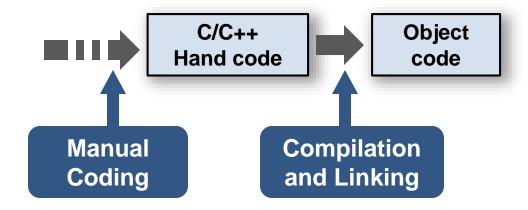

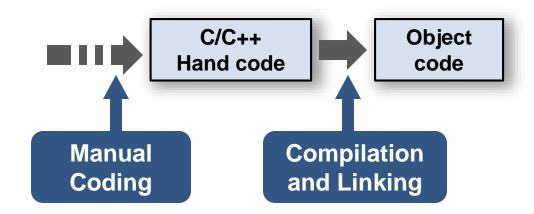

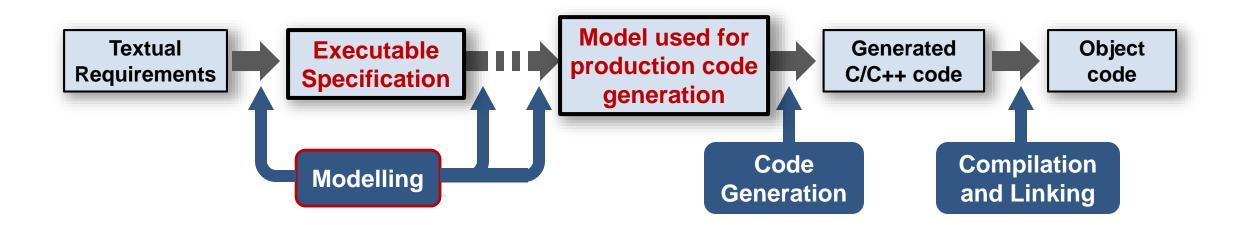

#### **Traditional Development Process**

#### **Models for Specification**

#### Model Abstraction – Work at an appropriate level of detail

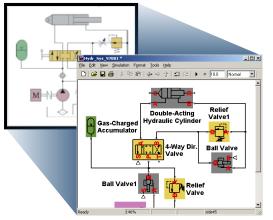

Simscape Fluids

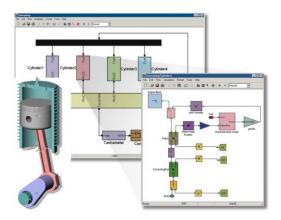

#### **Simscape Multibody**

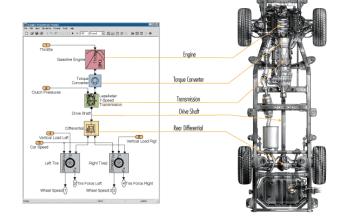

### Simscape Driveline

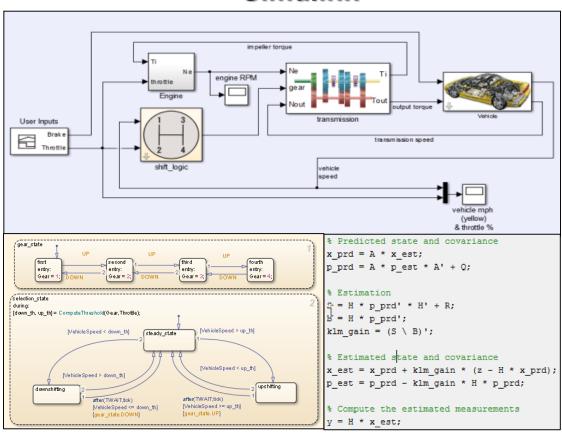

#### Simulink

**Stateflow**

**MATLAB**

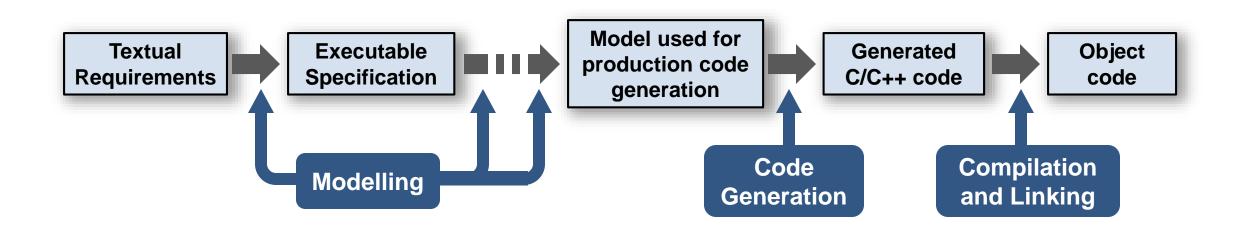

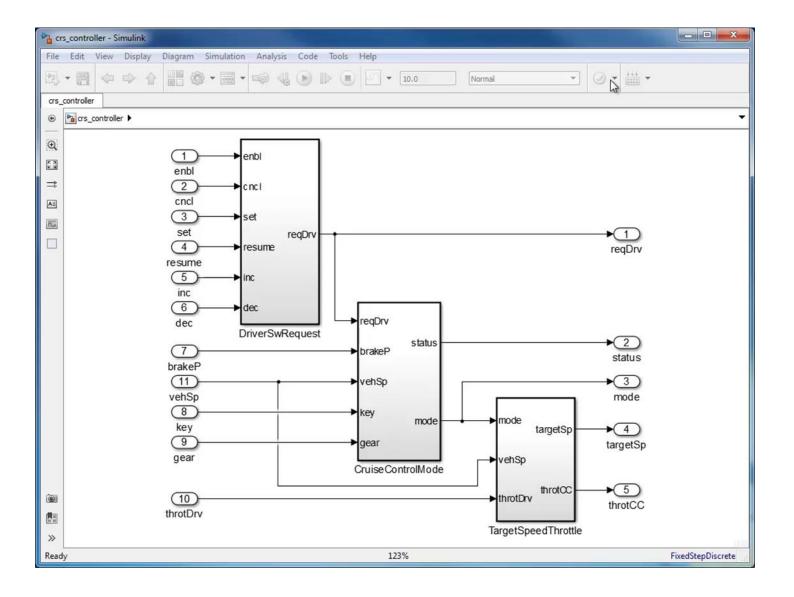

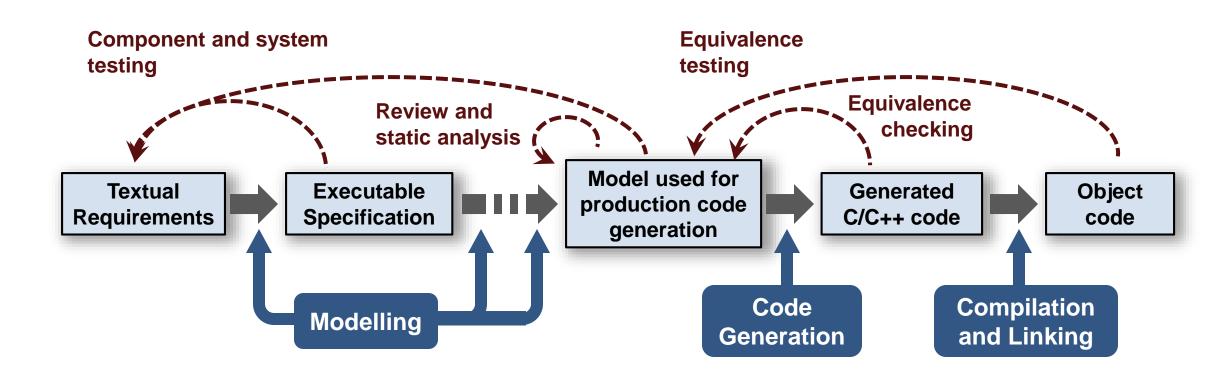

#### Complete Model Based Design Workflow, Concept to Code

#### Complete Model Based Design Workflow, Concept to Code

#### How do you ensure correctness?

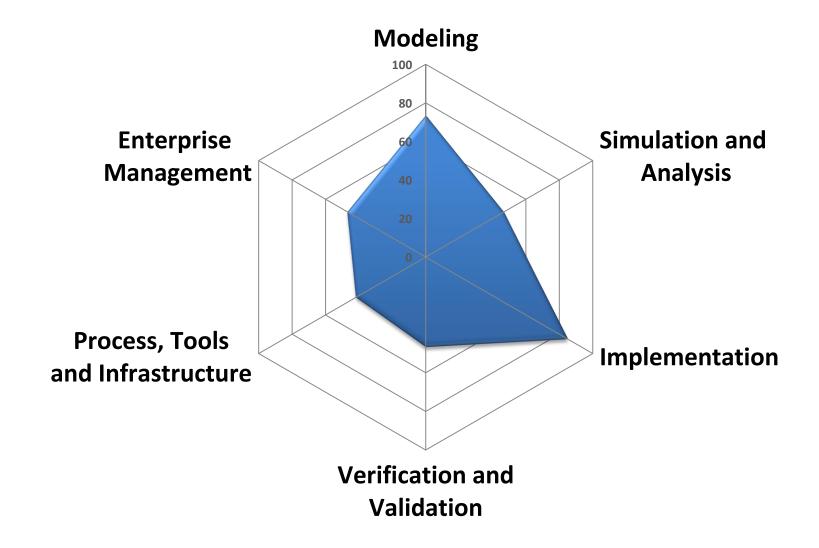

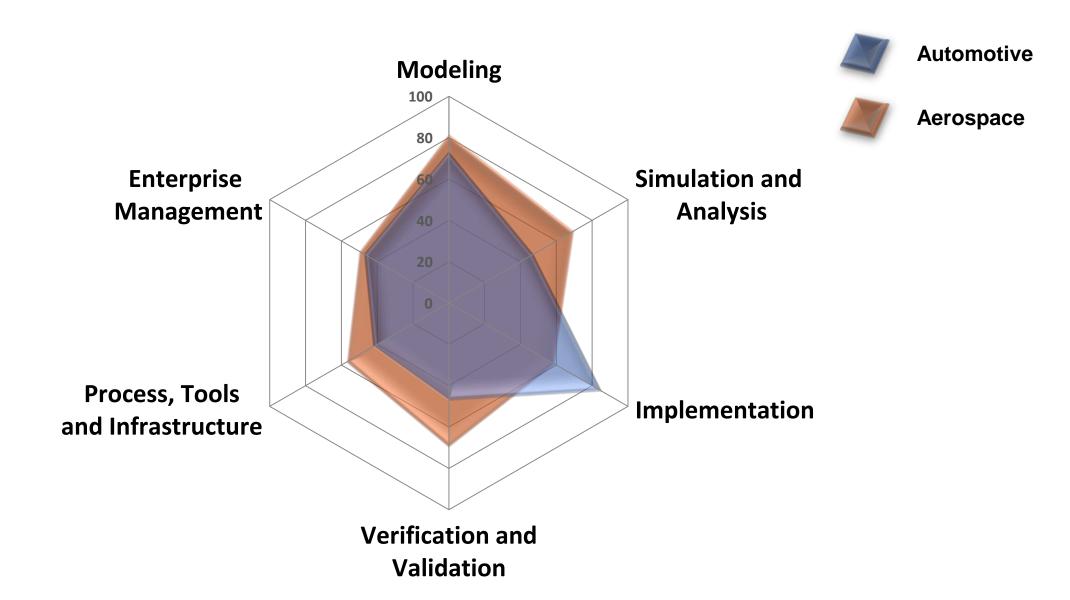

#### **Model-Based Design Maturity, Automotive Industry**

#### Model-Based Design Maturity, Automotive and Aerospace

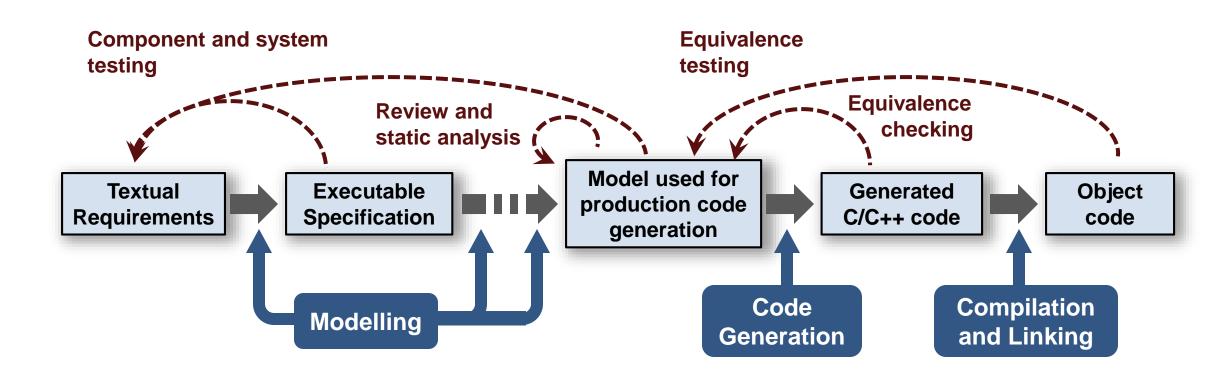

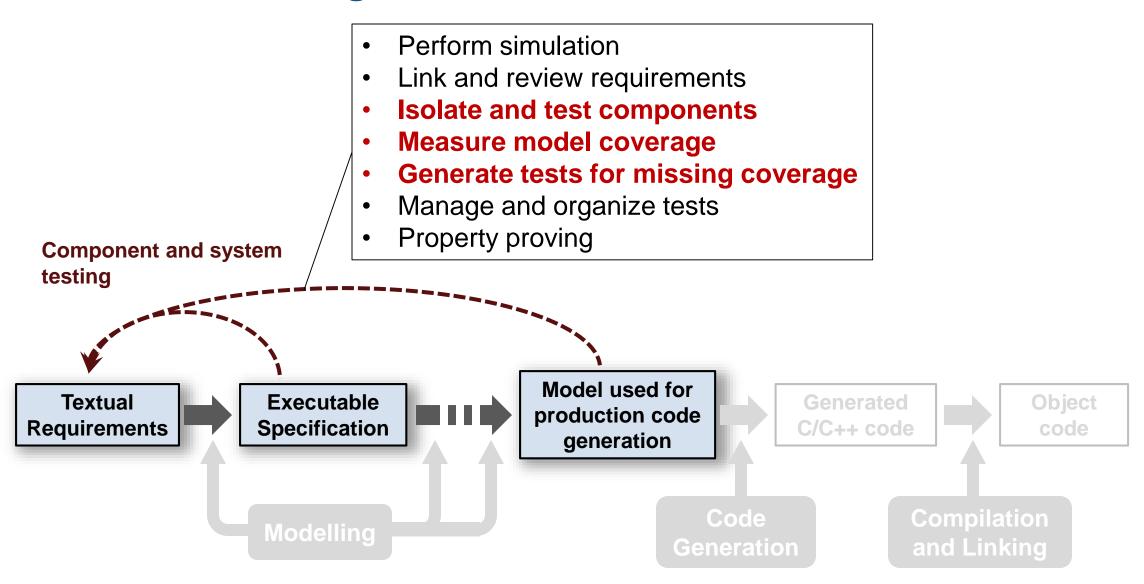

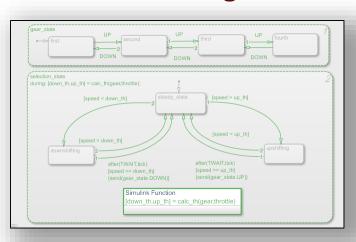

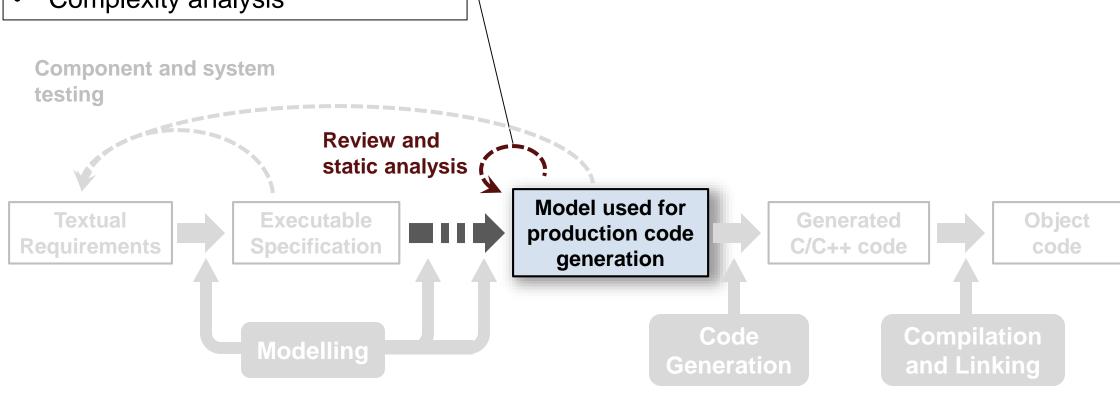

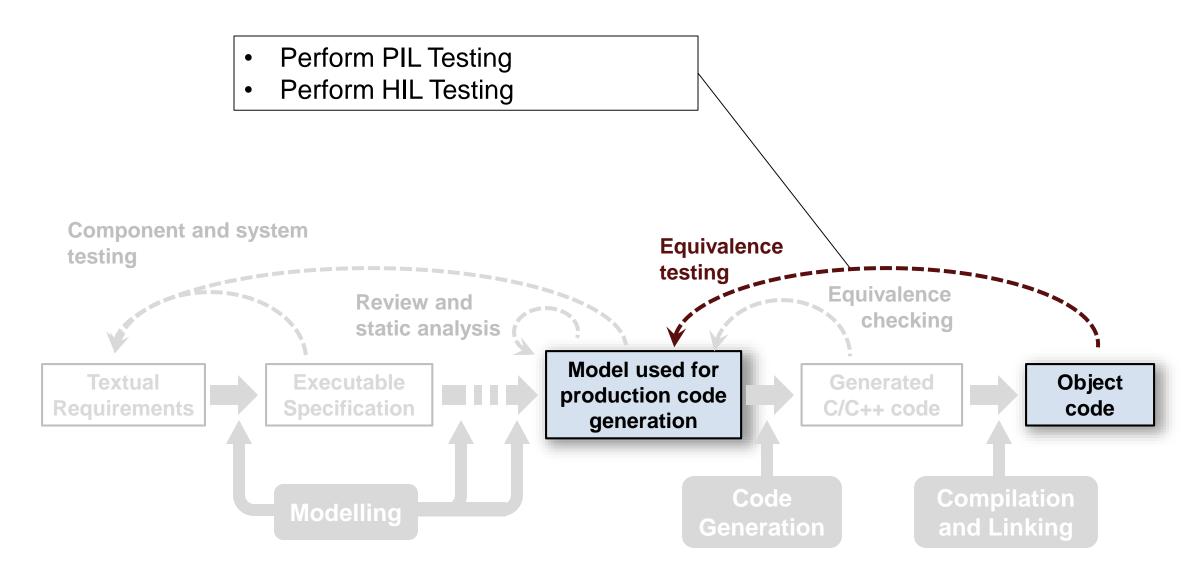

#### **Model Based Design Verification Workflow**

#### Model Based Design Verification Workflow

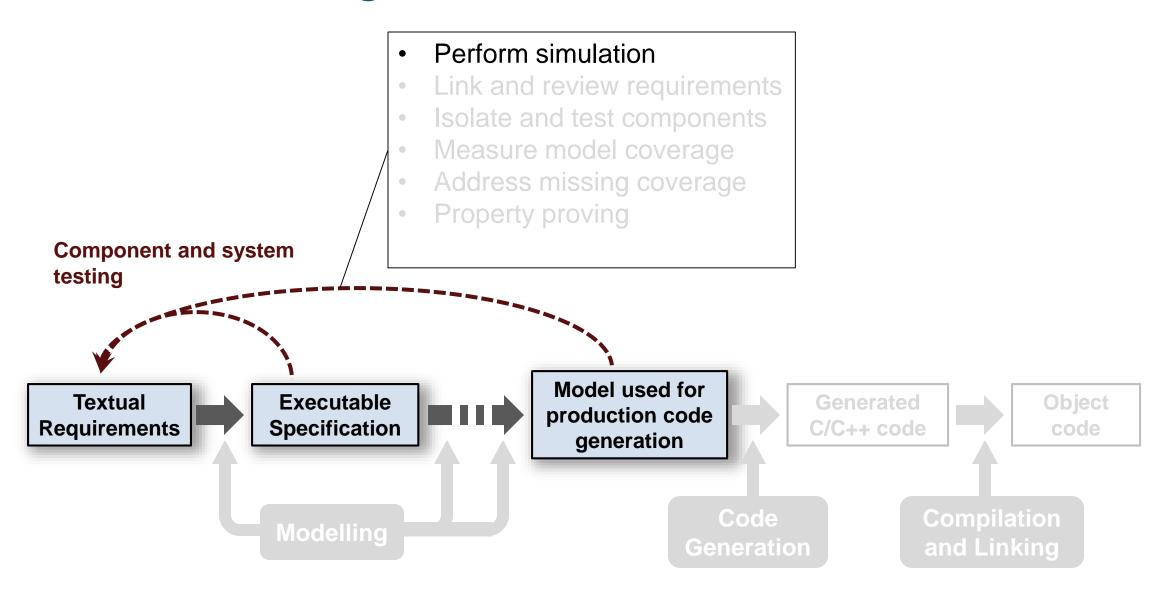

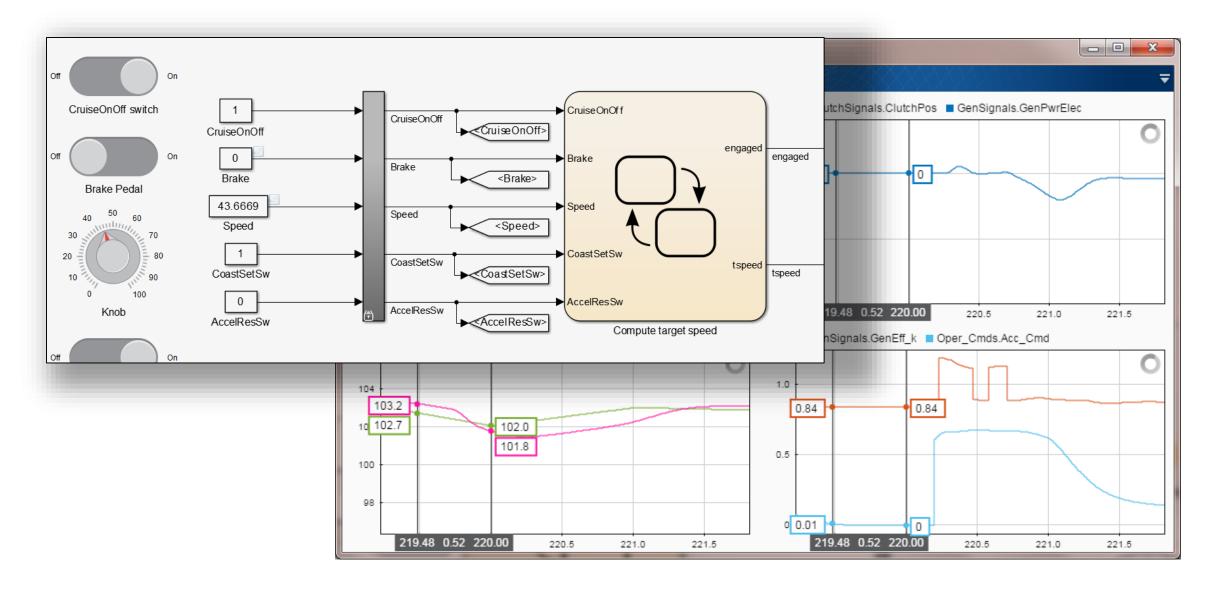

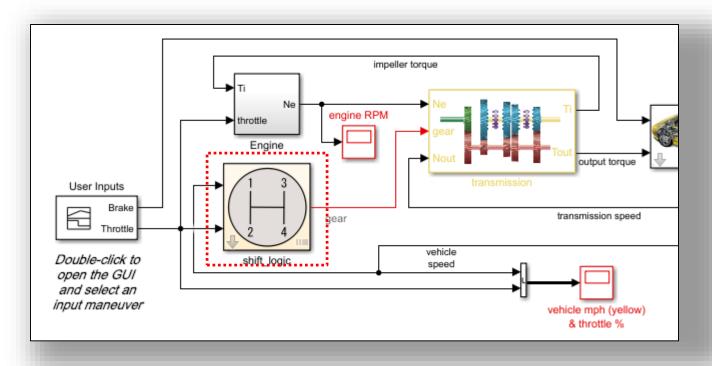

#### Ad-Hoc Simulation: Explore Behavior Virtually

#### Model Based Design Verification Workflow

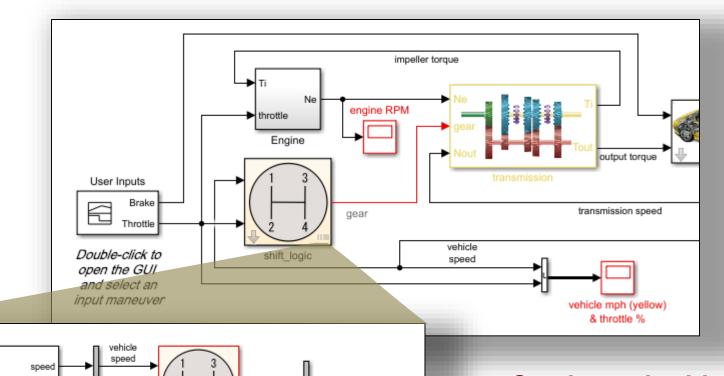

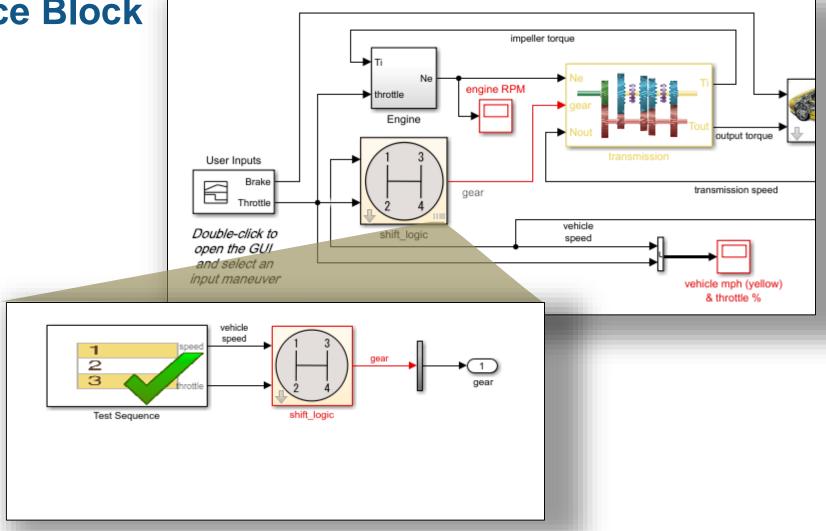

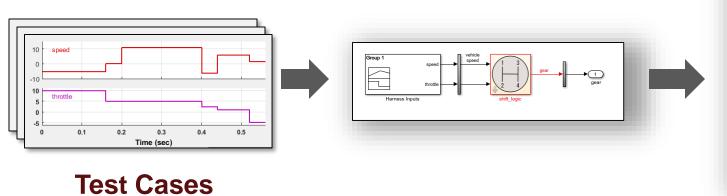

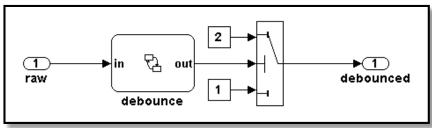

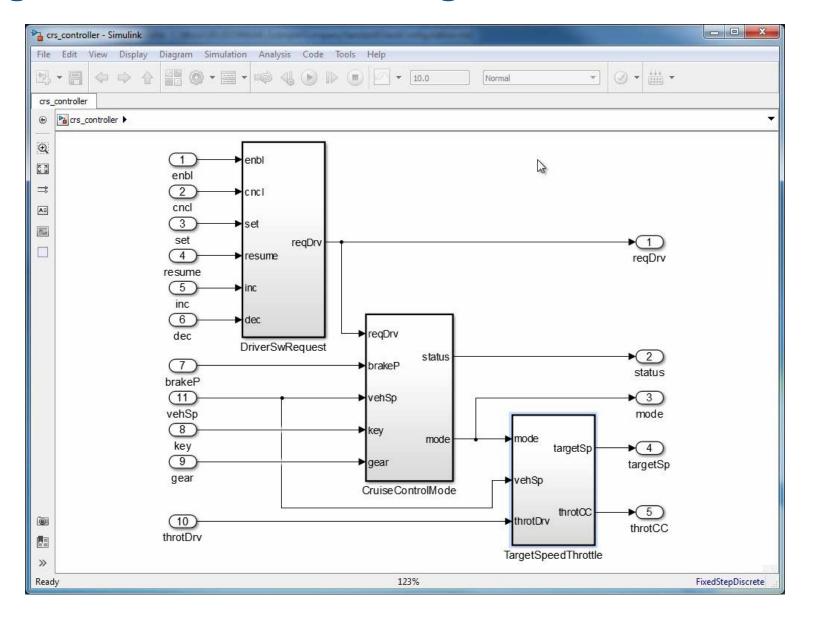

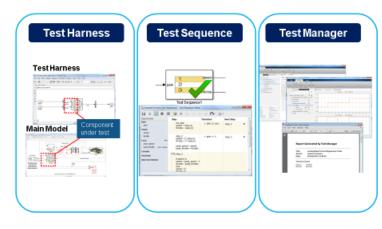

#### **Test Harnesses**

From <u>any</u> subsystem ...

#### **Test Harnesses**

From <u>any</u> subsystem ...

Isolate it with content it to drive inputs and analyze outputs

Group 1

throttle

Harness Inputs

Simulate independently

Can be embedded in design model file.

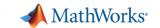

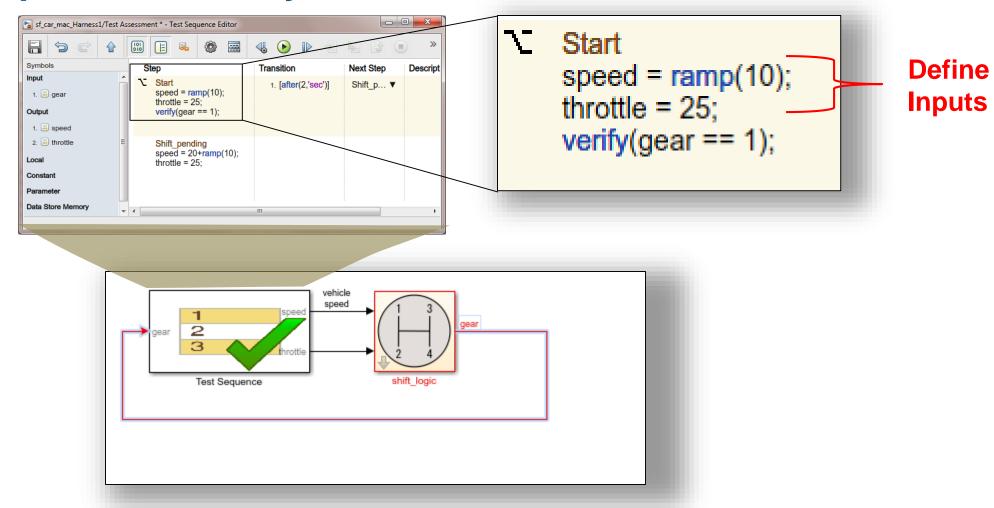

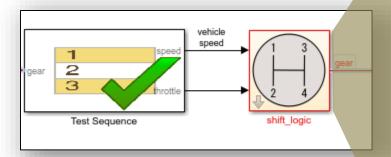

#### **Test Sequence Block**

A test sequence block can drive inputs

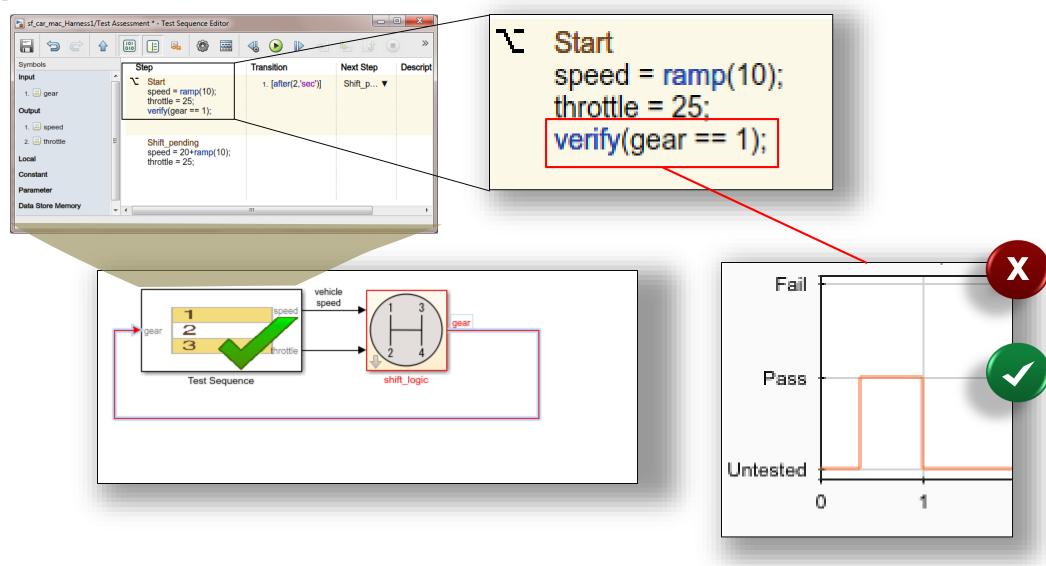

#### **Test Sequence Block**

A test sequence block can drive inputs and asses outputs

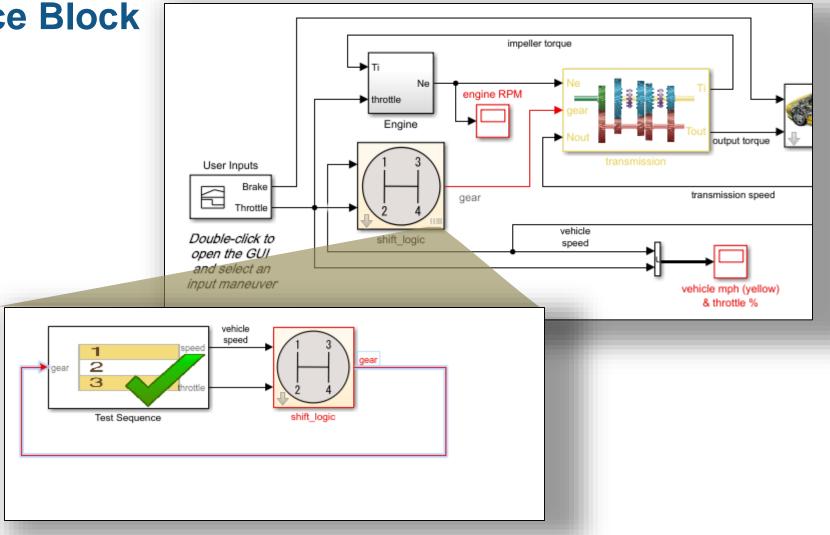

#### **Test Sequence Block Syntax**

#### **Test Sequence Block Syntax**

#### **Defining Pass/Fail Criteria**

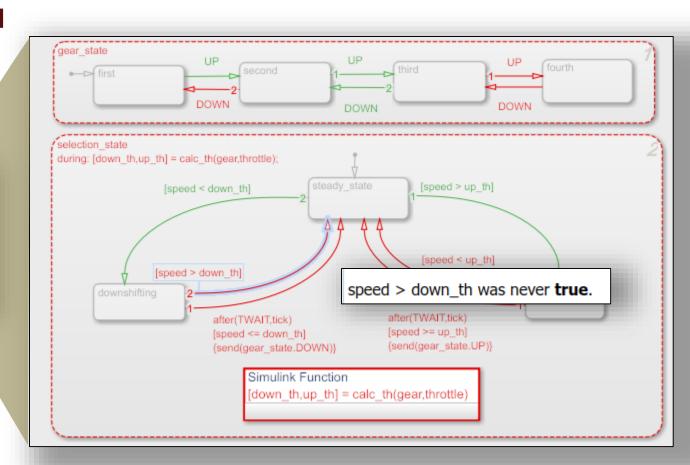

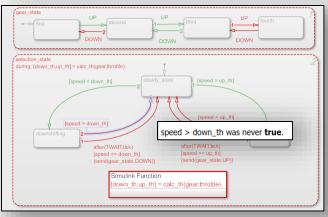

#### **Model Coverage**

#### **Identify testing gaps:**

Untested switch positions

Subsystems not executed

Transitions not taken

Many more ...

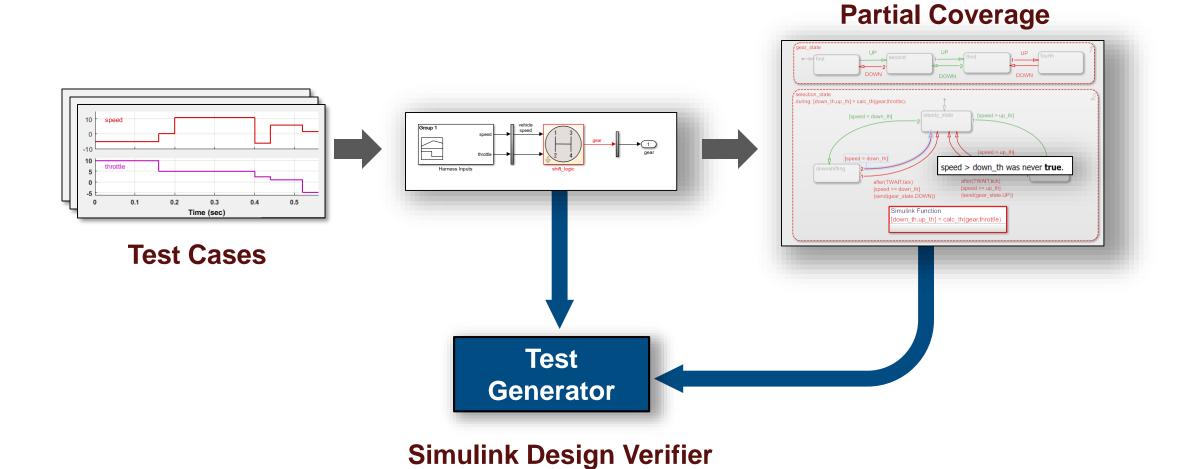

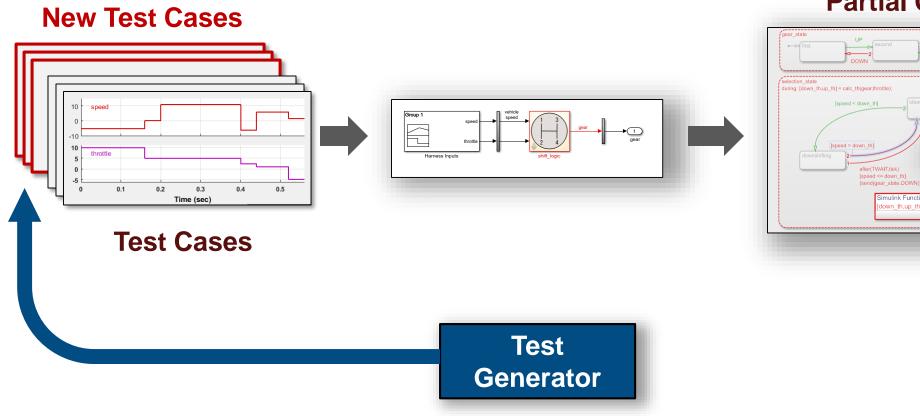

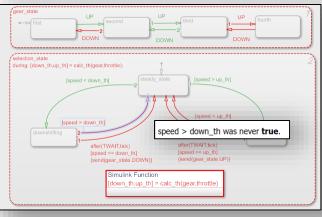

#### **Partial Coverage**

#### **Partial Coverage**

**Simulink Design Verifier**

# New Test Cases Test Cases

#### **Full Coverage**

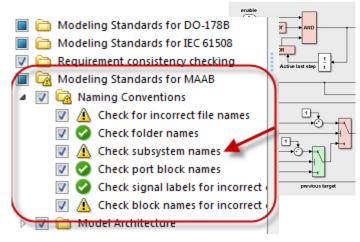

#### Model Based Design Verification Workflow

#### Model Based Design Verification Workflow

- Manual review

- Standards compliance checking

- Design error detection

- Complexity analysis

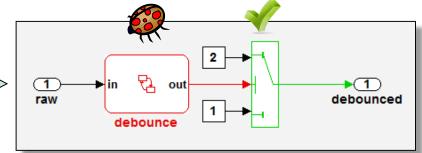

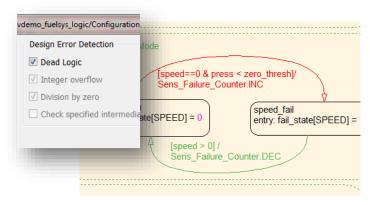

#### **Detecting Hidden Run-Time Design Errors**

**Design Model**

- Integer overflow

- Division by zero

- Array out-of-bounds

- Range violations

- Dead Logic

**Highlighted Model**

#### **Detecting Hidden Run-Time Design Errors**

#### **Detecting Hidden Run-Time Design Errors**

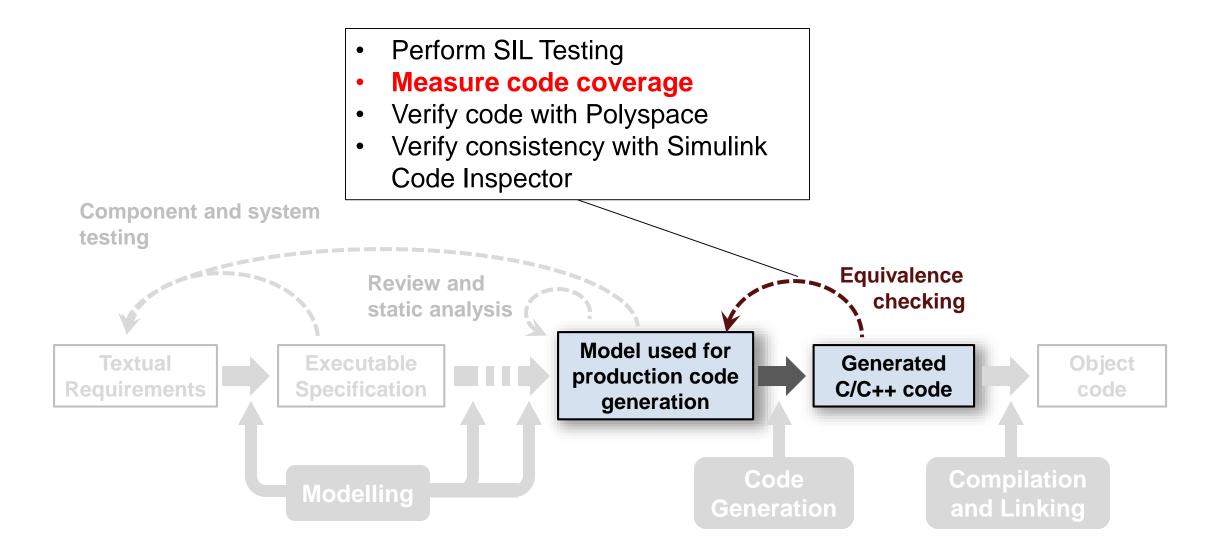

#### **Model Based Design Verification Workflow**

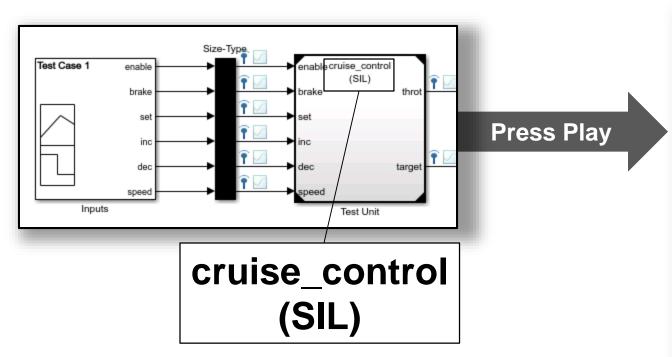

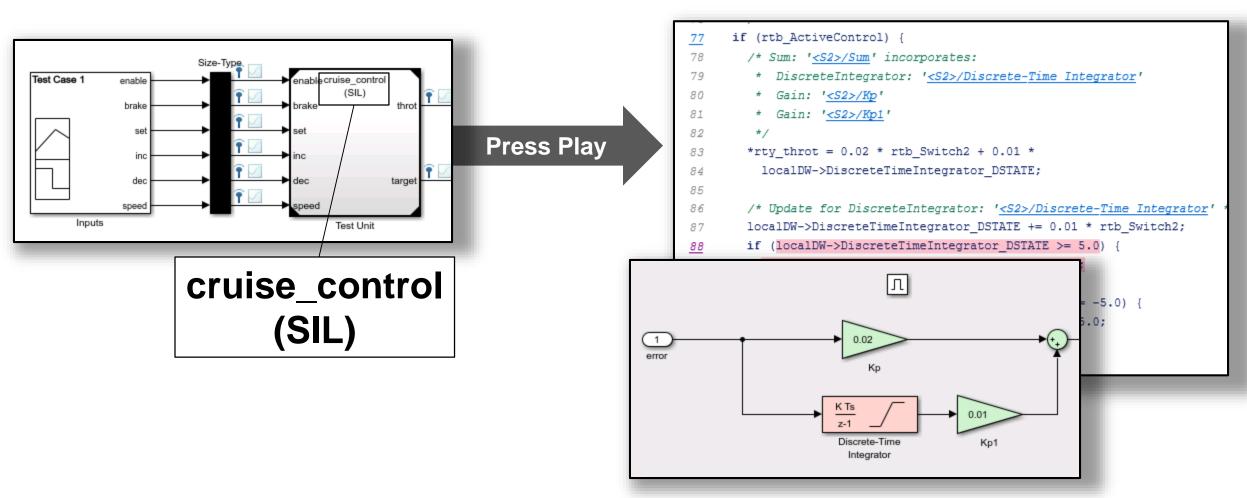

#### **Coverage for Generated Code (R2016a)**

```

if (rtb ActiveControl) {

/* Sum: '<S2>/Sum' incorporates:

* DiscreteIntegrator: '<S2>/Discrete-Time Integrator'

* Gain: '<S2>/Kp'

* Gain: '<S2>/Kp1'

*rty throt = 0.02 * rtb Switch2 + 0.01 *

localDW->DiscreteTimeIntegrator DSTATE;

84

85

/* Update for DiscreteIntegrator: '<S2>/Discrete-Time Integrator'

86

localDW->DiscreteTimeIntegrator DSTATE += 0.01 * rtb Switch2;

87

if (localDW->DiscreteTimeIntegrator DSTATE >= 5.0) {

localDW->DiscreteTimeIntegrator DSTATE = 5.0;

89

} else {

90

if (localDW->DiscreteTimeIntegrator DSTATE <= -5.0) {</pre>

localDW->DiscreteTimeIntegrator DSTATE = -5.0;

92

93

```

**Generated Code Coverage**

#### **Coverage for Generated Code (R2016a)**

Can also be highlighted on model

#### **Model Based Design Verification Workflow**

#### **Model Based Design Verification Workflow**

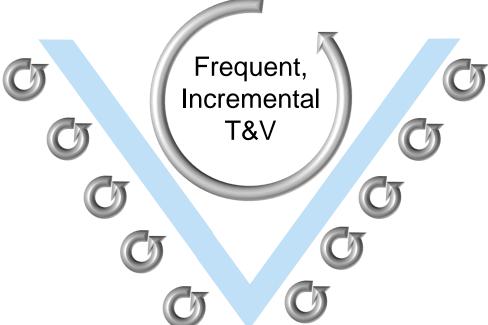

#### **Systematic Verification**

- Ensure that verification is systematically performed across:

- All requirements

- Complete model structure

- Complete code structure

- All design behaviors

Simulink Design Verifier

**Simulink Test**

Simulink Verification & Validation

#### **Test and Verification**

- Essential

Complex

Expensive - Pain Points

#### **Test and Verification**

- Essential → More Complete

- Expensive → Faster

- Complex  $\rightarrow$  Simpler

#### **Thank You!**