自上而下的合作

汇集多个技能在过程的早期

随着无线标准的发展和基础设施,必须开发新的系统和硬件在快速的时间轴。传统工作流划分责任,依靠规范文档防止多学科协作的类型需要按时提供新颖的产品。2022世界杯八强谁会赢?

-

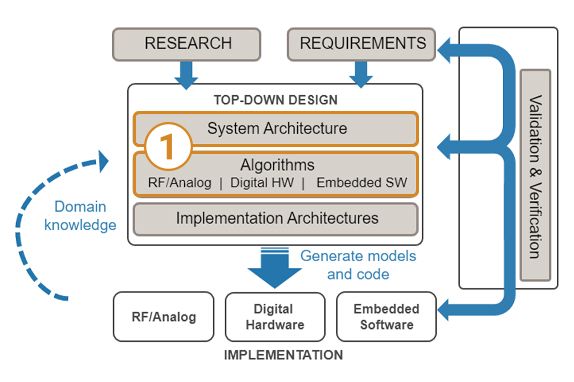

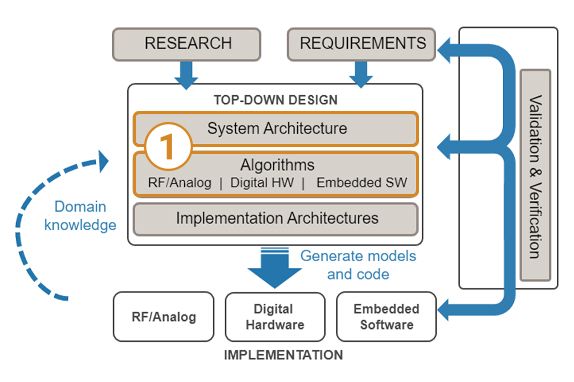

1。多畴的设计平台

汇集系统,算法,在视觉环境和特定领域的工程师合作探索和发展系统,算法和体系结构。模型你的天线、接收器放大器、ADC、DAC、调制/解调、纠错、和信号处理,以及核心数学和逻辑。

-

2。系统级仿真进行验证和验证

模拟整个系统从天线到比特来优化系统的吞吐量和早期检测和消除昂贵的问题。更高层次的抽象意味着有更少的细节来模拟,从而导致更快的运行时间和更容易调试。管理测试和跟踪功能覆盖之前确保健壮的验证原型和生产发展。

-

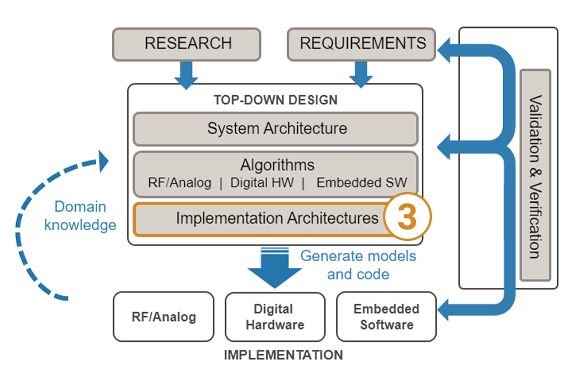

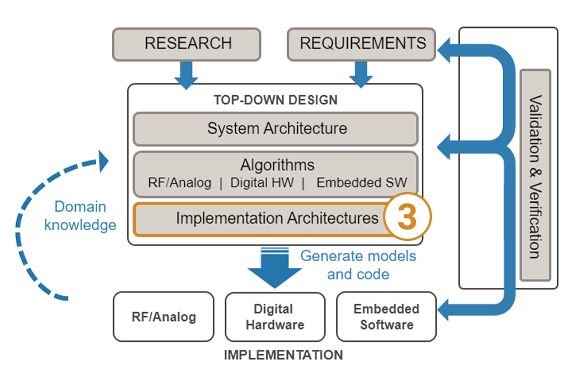

3所示。细化实现架构的能力

这种自上而下的方法使通信、DSP和硬件工程师,不断适应协作算法的比特流,权衡并行处理和资源使用情况,管理数据流的时间和延迟和平衡定点量化的数值精度和效率。他们可以使用相同的刺激模拟每个细化步骤算法设计,同时对算法比较结果和性能。

使用MathWorks已经启用诺基亚采用基于模型的设计和使用模型作为沟通的共同语言和自动化。

关键的外卖

- 启用多个领域专家之间的合作

- 模拟系统级行为早期检测和消除昂贵的问题

- 通过广泛的建筑探索提高质量

了解更多关于基于模型的设计

- 采用基于模型的设计,FPGA、ASIC和SoC发展

FPGA原型没有硬件描述语言(VHDL) / Verilog专长

目标和调试直接从MATLAB和Simulink FPGA原型硬件

原型设计无线通信算法在FPGA或软件定义无线电(SDR)硬件平台提供早期insight性能在实际操作条件,并经常作为一个关键示范检查点随着项目的进展向生产发展。传统原型工作流在稀缺的硬件设计工程师带来了沉重的负担,使用MATLAB®和仿真软件®使通信和DSP工程师在创建和调试更加自给自足FPGA原型。这种方法导致更快的迭代和得到一个工作原型用更少的时间和精力。

建模和模拟你的系统级算法后,可以逐步添加生活原型硬件元素。首先连接MATLAB和Simulink活无线收发器的原型模拟输入/输出。即使部署到原型设备,你可以保持联系MATLAB和Simulink进行分析和调试之前充分的实地测试。你可以很快开始使用通信工具箱为Xilinx™支持包®Zynq®的电台或者建立这种能力自己定制。

原型设计介绍了意料之外的现实世界的影响等干扰,从而导致设计故障或执行比预期的更差。您可以使用MATLAB仿真软件和高密度脂蛋白匹配分析和调试这些问题与设备直接连接或者通过捕获无线波形仿真使用。

“实施这一项目时,花了九个月四人。在我们评估我们救了约50 - 70%的时间而没有MATLAB参与和开始手动编写Verilog或VHDL代码”。

米哈伊尔•Galeev英特尔

关键的外卖

- 迭代和更快地进入一个工作原型

- 增加你的原型在数字硬件的能力

- 从MATLAB和Simulink内部分析和调试

请求一个免费试用

- 尝试HDL编码您的下一个项目原型设计fpga开发板。

Hardware-Proven设计知识产权

速度你的项目进度计划通过使用可配置的标准算法的硬件实现

无线通信严重依赖于标准信号协议、调制/解调方案,和纠错编码,以确保系统和设备的互操作性。在大多数情况下,这个标准功能并不区分您的应用程序,但你仍然需要将其集成到FPGA和ASIC。使用经过验证的知识产权(IP)的工程师们可以节省你的时间和精力,因此它们可以集中于开发和实现您的独特功能。

参考应用

使用现成的标准或定制为您的系统的功能

许多应用程序连接到5 g和LTE网络需要首先获得信号等信息寻找最强的细胞,检测中小学同步信号(PSS / SSS),和主恢复和系统信息块(MIB / SIB)。无线HDL工具箱™包括hardware-proven白盒这些子系统的实现,所以你可以把它们到你的设计或修改它们与任何你可能需要自定义功能。

IP块

硬件配置包括定点模型

无线通讯依赖的算法,如FFT、LDPC,极地,涡轮码,可以消耗大量的时间和精力来实现高效和正确的硬件。在自顶向下的流程,你可以建立你的设计使用这些现成的块。模拟硬件的行为,迅速调整的许多关键算法参数,然后生成synthesizable RTL。

自上而下的验证工作流程

重用更高抽象模型来验证实现

在传统的工作流中,工程师编写规范文档通常基于算法在MATLAB开发的。自顶向下的方法,使用MATLAB和Simulink工作流通过每个细化步骤保持连接。您可以使用相同的合成或捕获波形驱动框架黄金参考算法和直接stream-of-samples硬件实现和比较结果。

“我们这种方法保存至少一年的工程工作,这使我能够完整的实现自己不需要雇佣额外的数字工程师。”

马修·维纳射频像素

关键的外卖

- 节省硬件设计和验证的时间和精力用经过验证的IP

- 把你的硬件工程资源集中在你独特的功能

- 检查、调整和生成代码从抽象无线设计IP

了解更多

- 探索参考应用程序和设计IP块无线HDL工具箱。

硬件设计和验证的代码生成

探索和模拟硬件架构,然后自动生成特定项目的RTL和验证组件

依靠规范文档交流功能意图暴露风险疏忽和假设,很难适应变化。自顶向下的流程改进高级算法与硬件实现架构,允许方便地探索更多的选择,其次是高层验证。从那里你可以直接生成代码和模型开始生产硬件设计和验证。

之间的合作算法和硬件工程师

独立于目标HDL代码生成

SystemVerilog验证组件代

“我们增强团队之间的沟通,减少开发时间,和减少风险,评估系统性能在设计过程的早期。”

日立

关键的外卖

- 提高质量的探索范围广泛的硬件架构的选择

- 快速适应变化和新的需求重新生成代码

- 生成模型速度验证环境的创建

了解更多关于代码生成

- 生成一个5 g波形SystemVerilog验证。

你也可以从下面的列表中选择一个网站:

表现最好的网站怎么走吗

选择中国网站(中文或英文)最佳站点的性能。其他MathWorks国家网站不优化的访问你的位置。