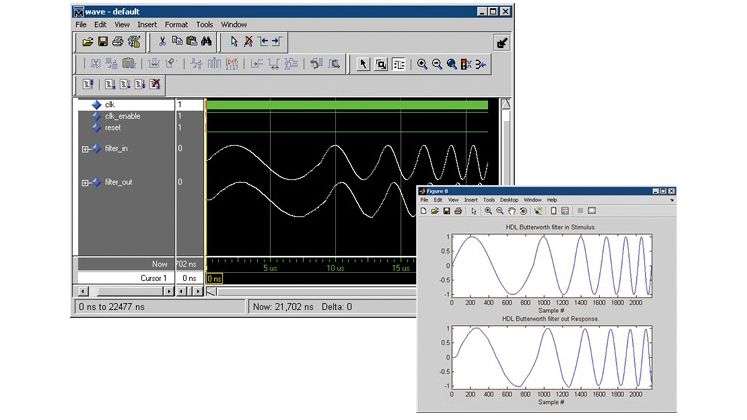

Filter Design HDL Coder™生成可合成的,便携式VHDL®和Verilog®用MATLAB设计的实现定点滤波器的代码®fpga或asic。它自动创建VHDL和Verilog测试台,用于模拟、测试和验证生成的代码。

开始:

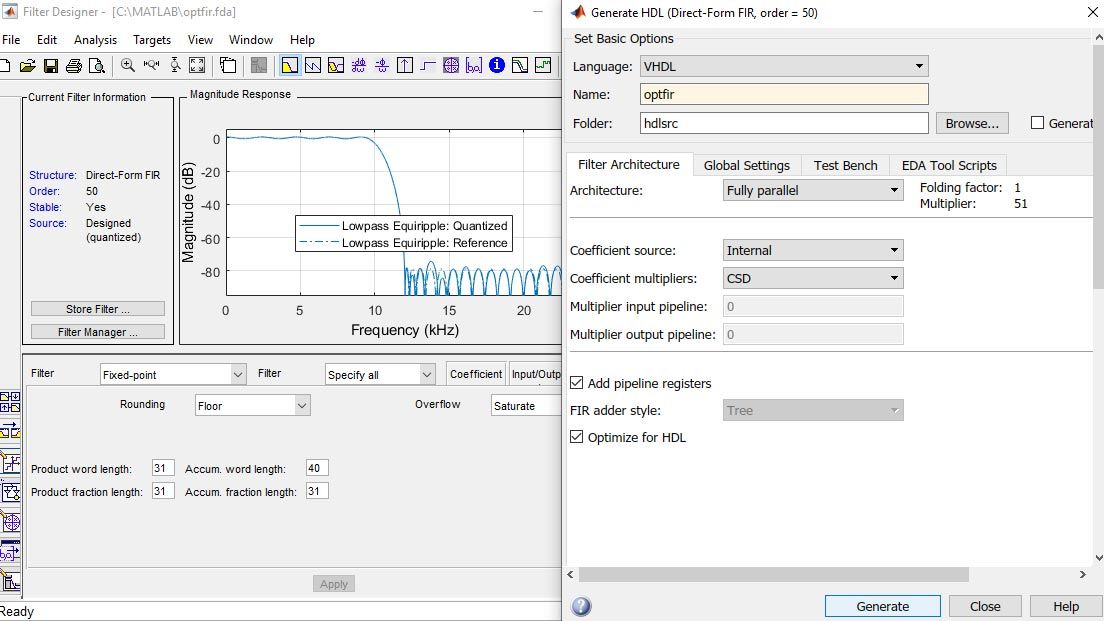

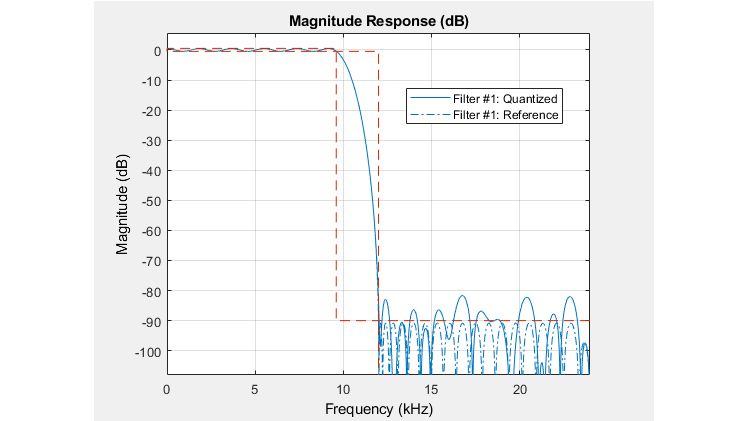

Filter Design HDL Coder™与DSP System Toolbox™集成,提供统一的设计和实现环境。您可以从MATLAB设计过滤器并生成VHDL和Verilog代码®命令行或从DSP系统工具箱使用过滤器设计器应用程序或过滤器生成器应用程序。

Filter design HDL Coder的设计条目输入是一个量化的过滤器,您可以通过以下两种方式之一创建:

Filter Design HDL Coder支持几个重要的过滤器结构,包括:

离散时间有限脉冲响应,包括对称结构、反对称结构和转置结构

二阶分段(SOS)无限脉冲响应(IIR),包括直接形式I、II和转置结构

多重速率的过滤器其中包括级联积分器-梳式(CIC)插补器和抽取器、直接式FIR和转置式FIR多相插补器和抽取器、FIR保持器和线性插补器以及FIR多相采样速率转换器结构

分数延迟滤波器,其中包括法罗结构

过滤器设计HDL Coder可以从级联多速率和离散时间滤波器生成HDL代码。这些单速率和多速率过滤器结构都支持定点和浮点(双精度)实现。此外,FIR结构支持无符号不动点系数。

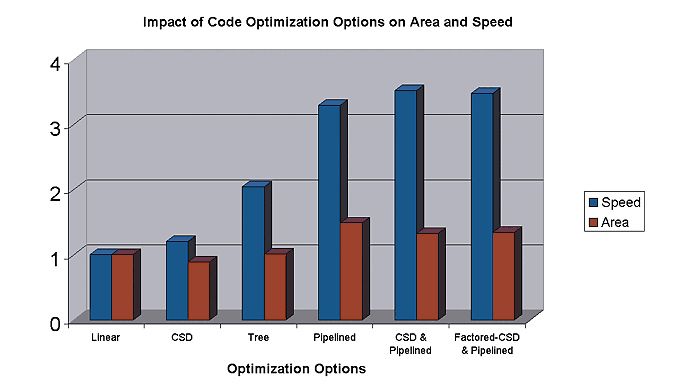

您可以从Filter Designer应用程序或Filter Builder应用程序为固定点过滤器生成VHDL或Verilog代码。当从任一应用程序生成HDL代码时,您可以设置HDL生成选项来指定实现架构,选择端口数据类型,插入管道寄存器等。其他选项允许您为过滤器HDL设计生成和配置测试平台。