开始高密度脂蛋白编码器

生成硬件描述语言(VHDL)而且VerilogFPGA和ASIC设计代码

HDL Coder™通过生成便携式、可合成的Verilog实现fpga、soc和asic的高级设计®和硬件描述语言(VHDL)®MATLAB代码®函数,仿真软件®模型和状态流®图表。您可以使用生成的HDL代码进行FPGA编程、ASIC原型设计和产品设计。

HDL Coder包括一个工作流顾问,可以在Xilinx上自动生成原型代码®,英特尔®,微芯片为ASIC和FPGA工作流程生成IP核。您可以优化速度和面积,突出显示关键路径,并在综合之前生成资源利用率估计。HDL Coder提供了您的Simulink模型和生成的Verilog和VHDL代码之间的可追溯性,支持遵守DO-254和其他标准的高完整性应用程序的代码验证。

安装与配置

教程

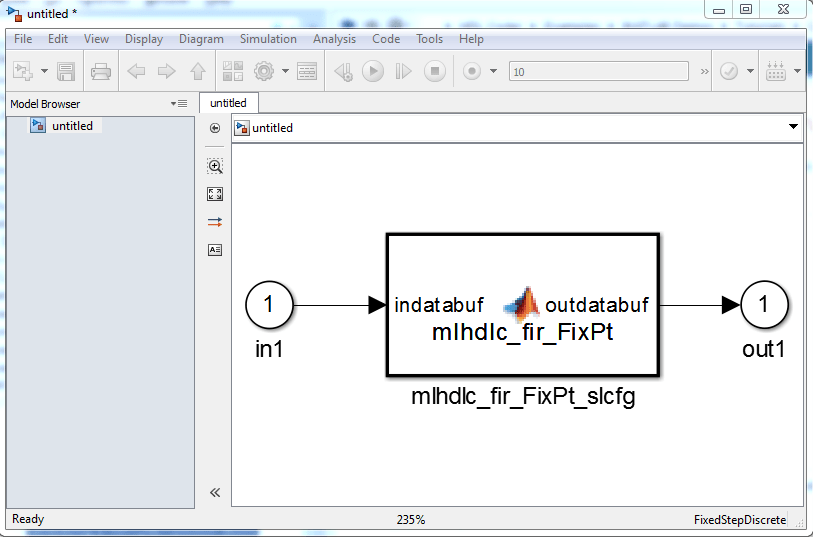

- 创建兼容hdl的Simulink模型

创建一个模型并检查HDL代码生成的兼容性。

- 从Simulink模型生成HDL代码

从Simulink模型生成VHDL和Verilog代码。

- 从Simulink模型验证生成的HDL代码

生成一个HDL测试平台来验证VHDL或Verilog代码。

- 基于Simulink模型的HDL代码生成和FPGA合成

在目标FPGA上生成代码并合成Simulink设计。

关于HDL代码生成

- 基本HDL代码生成工作流程

遵循从MATLAB和Simulink算法生成HDL代码和FPGA合成的工作流程。

- 在HDL编码器中时钟束信号的生成

HDL编码器如何在HDL代码中生成时钟,重置和时钟使能信号。

特色的例子

视频

HDL编码器概述

使用HDL编码器为FPGA和ASIC设计生成VHDL和Verilog代码

利用Simulink在FPGA或ASIC上部署MATLAB算法

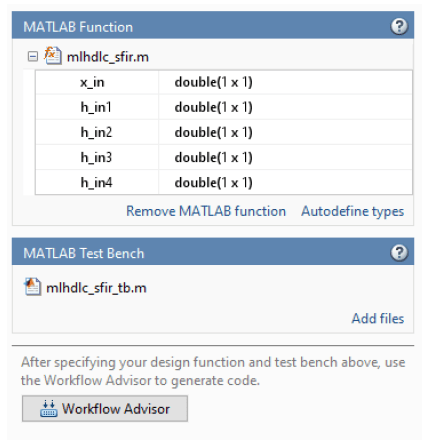

学习如何通过Simulink, Fixed-Point Designer™和HDL Coder获取MATLAB DSP算法,并针对FPGA或ASIC